Mengapa Deposisi dan Etsa Berada di Pusat Skalabilitas Chip

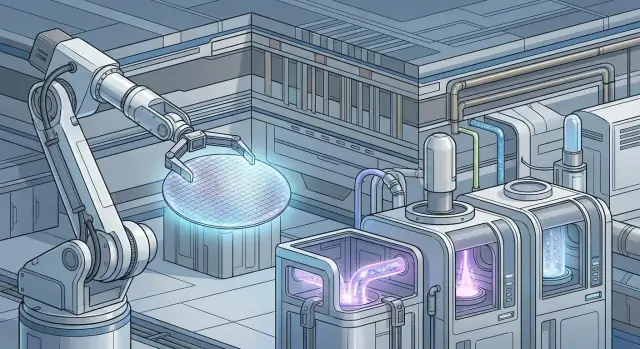

Jika Anda menyederhanakan pembuatan chip hingga gerakan yang paling berulang, dua aksi muncul berkali-kali: deposisi dan etsa.

Deposisi adalah langkah “menambah”. Peralatan meletakkan film ultra-tipis—konduktor, isolator, atau lapisan penghalang khusus—pada wafer, kadang hanya beberapa atom sekaligus. Etsa adalah langkah “menghapus”. Peralatan secara selektif mengukir material untuk membuat fitur kecil yang menjadi transistor dan jalur, idealnya tanpa merusak lapisan di bawahnya.

Seiring chip diskalakan, kedua langkah ini menjadi kenop utama yang digunakan insinyur untuk mengendalikan hal-hal yang paling penting pada dimensi nanometer: ketebalan, bentuk, dan antarmuka. Itulah mengapa perusahaan peralatan seperti Lam Research berada dekat dengan inti manufaktur leading-edge.

Apa arti “leading-edge” sebenarnya

“Leading-edge” umumnya mengacu pada node produksi volume tinggi yang paling maju—di mana densitas, daya, dan target performa paling agresif, dan margin kesalahan paling kecil. Ini bukan hanya angka pemasaran; ini tempat struktur perangkat baru dan material baru muncul pertama kali.

Keunggulan yang terakumulasi

Kemampuan alat penting (uniformitas, selektivitas, kontrol kerusakan, throughput). Tetapi pengetahuan proses sama pentingnya: resep, trik integrasi, umpan balik metrologi, dan pembelajaran dari cacat yang mengubah alat hebat menjadi proses pabrik stabil dengan yield tinggi.

Keunggulan itu berakumulasi lintas generasi teknologi karena setiap node baru tidak dimulai dari nol—ia membangun dari pembelajaran sebelumnya tentang bagaimana film tumbuh, bagaimana plasma berperilaku, dan bagaimana variasi kecil menyebabkan perubahan besar pada yield.

Apa yang akan kita bahas selanjutnya

Untuk melihat mengapa siklus deposisi dan etsa terus bertambah, kita akan melihat:

- Pematrian pada batas kemampuan dan mengapa loop “deposit–etsa–bersih” berulang itu umum

- Struktur 3D (fitur aspek rasio tinggi) yang lebih sulit diisi dan lebih sulit diukir

- Pembelajaran yield, cacat, dan variabilitas—di mana pengalaman terbayar

- Loop umpan balik antara pembuat alat dan fab yang mempercepat perbaikan

Dari Lapisan ke Logika: Bagaimana Chip Modern Sebenarnya Dibangun

Chip modern bukan “dipahat” dari blok silikon. Ia dirangkai—lebih mirip kue lapis mikroskopis—dengan berulang kali menambah film ultra-tipis, mempatternnya, dan secara selektif menghapus apa yang tidak diinginkan. Lakukan itu ratusan kali, dan Anda mendapatkan transistor, jalur, dan penghalang isolasi yang ditumpuk dan saling terkait dalam 3D.

Loop yang berulang: tambah, pattern, hapus

Secara garis besar, pembuatan chip berirama sebagai berikut:

- Deposisi meletakkan film (logam, oksida, nitrit, dan lainnya), sering hanya beberapa atom sampai beberapa nanometer tebal.

- Patterning menentukan di mana film itu harus tetap (menggunakan litografi untuk membuat masker).

- Etsa menghapus area yang terekspos, mentransfer pola ke dalam film.

Setiap loop menciptakan satu “irisan” dari perangkat akhir—struktur gerbang, lubang kontak, atau jalur interkoneksi—sampai logika dan memori chip muncul dari tumpukan.

Saat fitur diukur dalam nanometer satu digit, kontrol ketebalan dan bentuk berhenti menjadi “bagus untuk dimiliki.” Film yang sedikit terlalu tebal dapat menyumbat bukaan sempit; etsa yang sedikit terlalu agresif dapat melebar garis atau merusak lapisan di bawah. Perubahan profil kecil—sudut dinding samping, pembulatan sudut, kekasaran permukaan—dapat mengubah aliran listrik.

Langkah proses, jendela proses, dan yield

Manufaktur diorganisasikan menjadi langkah proses (operasi deposisi/etsa spesifik) yang harus berjalan di dalam jendela proses—rentang pengaturan di mana hasil konsisten dapat diterima. Saat chip menjadi lebih padat, jendela-jendela itu menyempit. Dan karena lapisan-lapisan berikutnya dibangun di atas yang sebelumnya, deviasi kecil dapat bereskalasi menjadi misalignment, short, open, dan akhirnya menurunkan yield.

Deposisi 101: Menempatkan Film dengan Kontrol Tingkat Atom

Deposisi adalah setengah “menambah material” dari pembuatan chip: membangun film ultra-tipis pada wafer sehingga langkah berikutnya bisa mempattern, melindungi, atau mengisolasi secara elektrik apa yang ada di bawah. Film-film ini bukan dekorasi—masing-masing dipilih untuk tugas tertentu, dan harus bekerja andal di milyaran fitur kecil.

Tiga pendekatan kerja: CVD, PVD, dan ALD

Chemical Vapor Deposition (CVD) menggunakan gas reaktif yang membentuk film padat pada permukaan wafer. Ini banyak digunakan untuk banyak lapisan dielektrik dan beberapa lapisan konduktif karena dapat menutup area besar secara efisien dan dengan uniformitas baik.

Physical Vapor Deposition (PVD) (sering disebut “sputtering”) menumbangkan atom dari target material dan mendepositkannya ke wafer. PVD umum untuk logam dan material hardmask, terutama ketika Anda menginginkan film yang padat—tetapi bisa kesulitan melapisi dinding samping struktur yang sangat dalam dan sempit.

Atomic Layer Deposition (ALD) mendeposit material satu “dosis” molekuler pada satu waktu melalui reaksi permukaan yang membatasi diri. Ia lebih lambat, tetapi unggul ketika kontrol dan penutup lebih penting daripada kecepatan—terutama untuk fitur 3D paling ketat.

Saat chip beralih ke fin, parit, dan lubang vertikal, deposisi berhenti menjadi masalah “melukis bagian atas”. Konformitas menggambarkan seberapa merata film melapisi permukaan atas, dinding samping, dan dasar sebuah fitur.

Jika lapisan tipis di dinding samping atau menyumbat di bukaan, Anda bisa mendapatkan kebocoran elektrik, pengisian buruk, atau kegagalan pada langkah etsa berikutnya. Konformitas tinggi krusial untuk fitur dalam dan sempit di mana margin kesalahan sangat kecil.

Properti film yang bisa menentukan yield

Bahkan jika ketebalan benar, film harus memenuhi beberapa persyaratan praktis:

- Uniformitas: ketebalan konsisten di seluruh wafer dan dari wafer ke wafer.

- Impuritas: atom tak diinginkan dapat mengubah perilaku elektrik atau menyebabkan masalah reliabilitas.

- Tegangan (stress): film yang terlalu tarik atau kompresif dapat melengkungkan struktur atau retak.

- Adhesi: lapisan harus menempel selama siklus temperatur, pembersihan, dan etsa.

Contoh intuitif: apa fungsi lapisan ini sebenarnya

- Liner melapisi dinding samping fitur untuk melindungi permukaan dan mengatur kondisi awal bagi pengisian berikutnya.

- Barrier mencegah logam berdifusi ke material sekitar (kritis untuk reliabilitas).

- Hardmask bertindak seperti stensil yang lebih tahan terhadap etsa agresif dibanding resist.

- Lapisan dielektrik mengisolasi secara elektrik dan memisahkan penghantar—penting untuk mencegah short.

Di leading-edge, deposisi bukan sekadar “menambah film.” Itu adalah rekayasa material presisi, disetel sehingga setiap etsa dan langkah pattern berikutnya berperilaku dapat diprediksi.

Etsa 101: Mengukir Fitur Tanpa Merusak yang Ada di Bawah

Etsa adalah setengah “subtraktif” dari pembuatan chip: setelah film dideposit dan dipattern dengan resist, etsa menghapus material terekspos untuk mentransfer pola itu ke lapisan di bawah. Triknya adalah Anda jarang ingin menghapus semuanya—Anda ingin menghapus satu material tertentu dengan cepat sambil berhenti pada material lain. Sifat ini disebut selektivitas, dan itu sentral mengapa fabs leading-edge menginvestasikan banyak pada pengetahuan proses etsa (dan mengapa vendor alat seperti Lam Research menyempurnakannya selama bertahun-tahun).

Mengapa selektivitas penting

Tumpukan modern mungkin mencakup silikon, silikon oksida, silikon nitrida, logam, dan hardmask. Saat etsa, Anda mungkin perlu membersihkan satu lapisan bersih-bersih sambil meninggalkan lapisan “etch stop” utuh. Selektivitas buruk dapat menipiskan lapisan kritis, menggeser dimensi transistor, atau menciptakan jalur kebocoran yang merugikan yield.

Etsa plasma, secara konseptual

Kebanyakan etsa canggih menggunakan plasma: gas tekanan rendah yang diubah menjadi spesies reaktif.

Dua hal terjadi bersamaan:

- Kimia: radikal reaktif membentuk produk samping volatil dengan material target (sehingga bisa dipompa keluar).

- Direksionalitas: medan listrik mempercepat ion ke wafer, memberi komponen “turun lurus” yang membantu mengukir parit sempit dan lubang kontak.

Menyeimbangkan keduanya adalah seni: terlalu banyak kimia dapat mengikis fitur ke samping; terlalu banyak energi ion dapat merusak apa yang Anda ingin pertahankan.

Seperti apa etsa yang “baik”

Tim proses biasanya mengejar beberapa hasil:

- Dinding samping vertikal (agar fitur sesuai bentuk yang dimaksud)

- Kerusakan minimal (kekasaran permukaan rendah, lebih sedikit muatan terperangkap, gangguan kristal lebih sedikit)

- Profil yang bisa diulang wafer-ke-wafer dan alat-ke-alat (agar langkah downstream berperilaku dapat diprediksi)

Tantangan umum pada etsa

Bahkan ketika resep “benar,” wafer nyata memberi perlawanan:

- Microloading: daerah pola padat dan jarang mengetsa pada laju berbeda.

- Footing/notching: distorsi profil dekat antarmuka atau lapisan etch-stop.

- Kekasaran: tekstur dinding samping yang dapat meningkatkan resistansi atau variabilitas.

- Residu: polimer atau material yang terdeposit ulang yang mengganggu deposisi atau pembersihan berikutnya.

Di node terdepan, mengelola detail ini sering menjadi perbedaan antara demo laboratorium dan produksi volume tinggi.

Pematrian pada Batas: Mengapa Siklus Etsa/Deposisi Terus Bertambah

Lacak pergeseran resep lebih cepat

Buat log perubahan resep dan tampilan 'apa yang berubah?' tanpa siklus pengembangan yang panjang.

Ketika orang membayangkan scaling chip, sering mereka membayangkan satu mesin terobosan yang “mencetak” garis yang semakin kecil. Pada praktiknya, transfer pola dibatasi oleh rantai lengkap—resist, hardmask, selektivitas etsa, tegangan film, dan pembersihan—bukan satu alat ajaib.

Hardmask stack: pola butuh penerjemah

Photoresist bagus untuk menangkap pola, tetapi biasanya terlalu tipis dan rapuh untuk bertahan etsa dalam dan presisi pada perangkat modern. Jadi fabs membangun hardmask stack—film yang dipilih hati-hati ditempatkan di atas lapisan target.

Alur sederhana:

- Deposit satu atau beberapa lapisan hardmask (sering material berbeda untuk selektivitas).

- Etsa pola resist ke hardmask.

- Etsa pola hardmask ke film bawah.

- Strip/clean, lalu ulangi bila perlu.

Setiap film yang dideposit dipilih bukan hanya untuk apa dirinya, tetapi bagaimana perilakunya saat etsa berikutnya: seberapa cepat ia teretsa dibanding lapisan tetangga, berapa banyak kekasaran yang dibuat, dan seberapa baik ia mempertahankan bentuknya.

Multi-patterning: satu fitur menjadi banyak langkah

Saat dimensi kritis menyusut melampaui apa yang dapat didefinisikan satu kali paparan litografi secara andal, fabs memakai multi-patterning—membagi satu pola padat menjadi beberapa eksposur dan transfer. Itu tidak hanya menambah langkah litografi; itu menggandakan loop deposisi/etsa penunjang untuk spacer, mandrel, trim, dan cut mask.

Intinya: “pola” pada chip leading-edge bisa jadi hasil dari beberapa siklus deposisi dan pengikisan yang dikendalikan ketat.

Mengapa penyetelan ujung-ke-ujung penting

Karena setiap langkah mengubah kondisi awal untuk langkah berikutnya, hasil terbaik datang dari menyetel urutan penuh—material, kondisi plasma, kebersihan kamar, dan pembersihan—sebagai satu sistem. Perbaikan kecil pada satu etsa bisa dihapus (atau diperbesar) oleh deposisi berikutnya, itulah sebabnya pengetahuan integrasi proses menjadi pembeda dari waktu ke waktu.

Transistor 3D dan Aspek Rasio Tinggi Meningkatkan Kesulitan

Transistor planar dulunya lebih “datar,” membuat banyak langkah terasa seperti melukis dan memotong permukaan. Scaling mendorong industri ke 3D: pertama FinFET (fin vertikal yang dibungkus oleh gate), dan kini konsep gate-all-around (GAA) di mana gate benar-benar mengelilingi channel (sering sebagai nanosheet bertumpuk).

Mengapa 3D mengubah deposisi

Begitu fitur punya dinding samping, sudut, dan rongga dalam, deposisi berhenti menjadi “melapisi bagian atas”. Film harus konformal—nyaris sama tebalnya di dasar parit seperti di permukaan atas.

Itulah mengapa teknik seperti ALD dan langkah CVD yang disetel dengan hati-hati menjadi lebih penting di leading-edge: beberapa atom terlalu tipis pada dinding samping bisa menjadi resistansi lebih tinggi, reliabilitas lebih buruk, atau penghalang lemah yang membiarkan material berdifusi ke tempat yang tidak seharusnya.

Mengapa 3D membuat etsa lebih pemilih

Etsa harus membentuk profil yang tepat: dinding lurus, dasar bersih, kekasaran minimal, dan penghapusan selektif satu material tanpa menggerogoti lapisan di bawah. Dalam pola 3D padat, over-etch kecil pun dapat melukai wilayah kritis, sementara under-etch meninggalkan residu yang menghalangi deposisi berikutnya.

Banyak struktur modern memiliki aspek rasio tinggi—sangat dalam dibanding lebar. Mendapatkan hasil seragam di miliaran fitur seperti itu sulit karena reaktan, ion, dan produk samping tidak bergerak rata masuk-keluar ruang sempit. Masalah seperti microloading dan kerusakan dinding samping menjadi lebih mungkin.

Material baru berarti permukaan baru

GAA dan interkoneksi canggih membawa tumpukan material yang lebih kompleks dan antarmuka ultra-tipis. Itu menaikkan standar untuk persiapan permukaan: pre-clean, perlakuan plasma lembut, dan kontrol antarmuka sebelum deposisi berikutnya. Ketika “permukaan” hanya beberapa lapis atom tebal, pengetahuan proses menjadi pembeda antara perangkat yang berfungsi dan yang diam-diam gagal kemudian hari.

Yield, Cacat, dan Variabilitas: Di Mana Pengetahuan Proses Membayar

“Yield” sederhana saja: bagian dari chip pada wafer yang bekerja seperti dimaksudkan. Jika sebuah wafer memuat ribuan chip, perubahan kecil pada tingkat cacat bisa berarti ratusan bagian yang bisa dijual lebih banyak. Itulah mengapa produsen mengobsesi angka-angka kecil—karena pada skala besar, perbaikan kecil berubah menjadi output nyata.

Bagaimana cacat menjadi masalah elektrik

Banyak kerugian yield tidak tampak dramatis di bawah mikroskop; mereka muncul sebagai kegagalan elektrik. Beberapa contoh umum:

- Opens: sebuah jalur menipis atau putus, sehingga arus tidak bisa mengalir.

- Shorts: dua fitur yang seharusnya terpisah bersentuhan, menciptakan koneksi tak diinginkan.

- Leakage: lapisan isolasi ternyata terlalu tipis, berpori, atau rusak, membiarkan arus “membocor”.

Langkah deposisi dan etsa dapat mempengaruhi semua ini. Film yang sedikit meleset dalam ketebalan, komposisi, atau uniformitas mungkin masih “terlihat baik”, tetapi dapat menggeser perilaku transistor cukup jauh sehingga melampaui target kecepatan atau daya.

Variabilitas: pembunuh yield yang sunyi

Bahkan ketika tidak ada cacat jelas, variasi di seluruh wafer (atau dari wafer ke wafer) menciptakan chip yang berperilaku tidak konsisten. Satu pojok berjalan lebih panas, pojok lain lebih lambat, dan tiba-tiba pengelompokan produk berubah—atau part gagal. Kontrol ketat atas laju deposisi, kondisi plasma, dan selektivitas etsa mengurangi fluktuasi ini.

Metrologi dan inspeksi sebagai kemudi

Fabs modern tidak menyetel proses berdasarkan intuisi. Mereka bergantung pada metrologi (mengukur ketebalan, dimensi kritis, bentuk profil, uniformitas) dan inspeksi (menemukan partikel, cacat pola, masalah tepi). Hasilnya memberi umpan balik ke penyesuaian proses:

- Jika profil bergeser, kimia etsa atau timing disetel ulang.

- Jika film bervariasi ketebalannya, parameter deposisi dikoreksi.

- Jika tanda-tanda cacat melonjak, insinyur menelusuri sumbernya ke modul tertentu, kondisi kamar, atau lot material.

Dalam praktiknya, ini juga menciptakan masalah perangkat lunak: menyatukan data dari alat, metrologi, dan inspeksi menjadi sesuatu yang bisa diambil tindakan dengan cepat. Tim sering membangun dashboard internal, sistem pemberitahuan, dan alat “apa yang berubah?” untuk mempersingkat loop dari sinyal ke perbaikan. Platform seperti Koder.ai dapat membantu di sini dengan membiarkan tim proses dan data membuat web app ringan dari chat—berguna untuk mengintegrasikan KPI yield, catatan ekshursi, dan riwayat run tanpa menunggu siklus pengembangan tradisional yang lama.

Pembelajaran terakumulasi lintas node

Pengetahuan paling berharga bersifat incremental: setiap node mengajarkan apa yang menyebabkan cacat tertentu, pengaturan mana yang bergeser seiring waktu, dan kombinasi mana yang stabil. Pelajaran-pelajaran itu terbawa maju—jadi node berikutnya dimulai dengan playbook yang lebih baik, bukan lembar kosong.

Resep, Reproduksibilitas, dan Permainan Jangka Panjang Pengembangan Proses

Ubah fab data menjadi aplikasi

Buat dashboard yield dan excursion sederhana dari chat, lalu deploy saat dibutuhkan.

Alat deposisi atau etsa tidak berjalan dengan satu “setting” tunggal. Ia berjalan dengan resep—urutan terstruktur langkah yang mendefinisikan bagaimana proses terjadi sepanjang waktu. Sebuah resep dapat mencakup beberapa fase (stabilisasi, pre-clean, langkah utama, perlakuan pasca), masing-masing dengan aliran gas, tekanan, temperatur, daya RF, timing, dan logika endpoint sendiri. Ia juga mencakup detail “sunyi”: waktu purge, perilaku pemegangan wafer, dan bagaimana kamar disiapkan sebelum wafer pertama.

Mengapa resep terus berubah

Saat chip pindah ke node baru, fabs memperkenalkan material baru dan bentuk 3D baru—seringkali bersamaan. Film yang bekerja pada permukaan datar mungkin berperilaku berbeda pada fitur dalam dan sempit. Langkah etsa yang cukup selektif di generasi lalu bisa mulai merusak liner atau barrier yang baru diperkenalkan.

Itulah mengapa resep berevolusi: target perangkat bergeser (kecepatan, daya, reliabilitas), geometri semakin ketat, dan batasan integrasi bertambah. Pengembangan proses menjadi siklus panjang penyetelan, pengukuran, dan penyetelan ulang—kadang untuk menyelesaikan masalah yang hanya muncul setelah ribuan wafer diproses.

Reproduksibilitas, pencocokan, dan tetap bersih

Dalam manufaktur volume tinggi, tidak cukup satu kamar menghasilkan hasil bagus sekali. Reproduksibilitas berarti resep yang sama memberikan hasil yang sama wafer demi wafer. Pencocokan alat-ke-alat berarti resep yang dipindahkan ke alat lain (atau fab lain) tetap mencapai ketebalan, profil, dan uniformitas yang sama dalam batas ketat—kalau tidak perencanaan produksi dan yield menderita.

Kontrol kontaminasi bagian dari realitas ini. Kamar “menjadi tua” saat film menumpuk pada permukaan internal, mempengaruhi kondisi plasma dan risiko partikel. Fabs mengandalkan conditioning kamar, run penggaraman, pembersihan, dan jadwal pemeliharaan preventif agar proses tetap stabil sepanjang waktu. Pengetahuan operasional—cara menjaga resep berperforma selama berbulan-bulan, bukan menit—adalah tempat pengalaman terakumulasi.

Mengapa Pembuat Alat dan Fabs Melakukan Ko-Optimisasi, Bukan Bekerja di Silo

Chip leading-edge tidak diproduksi hanya dengan membeli alat, memasangnya, lalu menekan “run.” Langkah deposisi dan etsa terkait erat dengan layout chip, tumpukan material, dan target reliabilitas, sehingga orang yang membangun peralatan dan yang menjalankan fab berakhir melakukan iterasi bersama.

Serah terima adalah loop, bukan garis lurus

Perancang chip mendefinisikan struktur yang dibutuhkan (misalnya kontak lebih kecil, via lebih tinggi, stack logam baru). Tim integrasi proses di dalam fab menerjemahkan desain itu menjadi alur langkah demi langkah: deposit lapisan ini, pattern, etsa, bersihkan, ulangi. Pembuat alat seperti Lam Research kemudian membantu mengubah kebutuhan itu menjadi resep yang dapat diproduksi pada perangkat keras nyata.

Serah terima itu cepat berubah menjadi loop: run awal mengungkap masalah (drift profil, residu, kekasaran tepi garis, kerusakan tak terduga), dan umpan balik kembali ke alur proses dan pengaturan alat—kadang bahkan ke opsi perangkat keras seperti material kamar, sumber plasma, atau delivery gas.

Ko-optimisasi lintas material, perangkat keras, dan alur

Di leading-edge, Anda tidak bisa mengoptimalkan deposisi atau etsa secara terpisah karena setiap langkah mengubah kondisi awal langkah berikutnya. Pergeseran kecil pada densitas film bisa mengubah laju etsa; etsa yang lebih agresif bisa membuat deposisi downstream kurang konformal. Ko-optimisasi menyelaraskan:

- Pilihan material (dielektrik baru, hardmask, lapisan barrier)

- Kapabilitas alat (kimia plasma, kontrol temperatur, penanganan wafer)

- Urutan proses (siklus etsa/deposisi multi-langkah, pembersihan, titik metrologi)

Trade-off nyata—dan dikelola dengan sengaja

Fabs terus menyeimbangkan throughput vs. presisi: proses lebih cepat dapat meningkatkan variabilitas, sementara kontrol ultra-ketat bisa mengurangi wafer per jam. Demikian pula, selektivitas vs. kerusakan adalah ketegangan berulang: etsa yang sangat selektif mungkin memerlukan kondisi lebih keras yang berisiko menambah kekasaran atau cacat.

Dukungan integrasi adalah bagian dari produk

Bagian penting dari nilai yang diberikan adalah dukungan integrasi berkelanjutan—troubleshooting di tempat, mencocokkan performa antar kamar, mengurangi ekskursi, dan membantu pemulihan cepat saat yield berubah. Untuk manufaktur volume tinggi, kemitraan semacam itu bisa sama pentingnya dengan spesifikasi alatnya.

Dari Kapabilitas Alat ke Output Fab: Reliabilitas dan Uptime Penting

Miliki kode sumber

Pertahankan fleksibilitas dengan mengekspor kode sumber kapan pun Anda perlu memperluas atau memigrasi.

Alat deposisi atau etsa bisa tampak hebat di lembar spesifikasi—sampai ia harus berjalan 24/7, pada ribuan wafer, dengan hasil yang sama setiap kali. Dalam produksi volume tinggi, reliabilitas dan uptime bukanlah "bagus untuk dimiliki." Mereka langsung menentukan berapa banyak wafer bagus yang bisa dikirimkan fab.

Kontrol ketat adalah tujuan utama

Deposisi dan etsa hidup dan mati oleh stabilitas proses. Drift kecil dalam aliran gas, tekanan kamar, daya plasma, atau temperatur dapat menggeser ketebalan film, sudut dinding samping, atau tingkat kerusakan—mengubah resep yang bekerja menjadi kehilangan yield.

Itulah mengapa alat terdepan (termasuk sistem Lam Research) berinvestasi berat pada perangkat keras yang dapat diulang: suplai RF stabil, kontrol aliran massa presisi, manajemen termal, dan sensor yang dapat menangkap ekskursi lebih awal.

Output bergantung pada pemeliharaan sama seperti fisika

Bahkan bila proses sempurna, produksi terganggu saat alat sering turun. Output fab nyata dibentuk oleh:

- Jadwal pemeliharaan terencana (pembersihan, seasoning kamar, penggantian kit)

- Downtime tak terencana (peristiwa partikel, instabilitas plasma, masalah pompa)

- Logistik suku cadang (memiliki consumable yang tepat di lokasi, bukan macet di transit)

Alat yang lebih mudah diservis—dan didukung oleh perencanaan suku cadang yang kuat—menjaga lebih banyak kamar berjalan dan lebih banyak lot bergerak.

Reliabilitas menjadi biaya dan jadwal

Uptime lebih tinggi biasanya menurunkan biaya per wafer: lebih sedikit operator menganggur, pemanfaatan ruang bersih mahal lebih baik, dan lebih sedikit waktu hilang untuk rework. Sama pentingnya, ketersediaan yang konsisten membuat jadwal pengiriman dapat diprediksi, yang penting ketika langkah downstream sangat terantri.

Satu realitas lagi: scaling dari demo lab ke produksi massal memberi tekanan berbeda pada alat. Run diperpanjang, starts wafer lebih tinggi, dan anggaran cacat lebih ketat dengan cepat mengekspos titik lemah—jadi rekayasa reliabilitas menjadi bagian inti dari “kapabilitas proses.”

Apa yang Perlu Diwaspadai Selanjutnya: Tekanan Skalabilitas dan Bottleneck Proses Berikutnya

Saat chip mendorong ke node yang lebih kecil dan struktur 3D lebih banyak, kemajuan semakin bergantung pada pengulangan langkah deposisi dan etsa dengan presisi ekstrem—sering ratusan kali dalam satu tumpukan perangkat. “Bottleneck” berikutnya biasanya bukan satu terobosan, melainkan kesulitan kumulatif menjaga setiap siklus konsisten sambil mempertahankan yield, mengendalikan variabilitas, dan meramp-up proses baru cukup cepat untuk memenuhi permintaan.

Di mana tekanan terkonsentrasi

Beberapa tren kemungkinan akan memberi tekanan terbesar pada deposisi/etsa:

- Arsitektur perangkat baru (GAA/nanosheet, CFET): ruang lebih ketat dan lapisan lebih tipis meningkatkan sensitivitas terhadap kesalahan ketebalan film atau kedalaman etsa.

- Backside power delivery: menambah permukaan baru, langkah integrasi baru, dan mode kegagalan baru yang harus dikelola tanpa merusak perangkat sisi depan.

- Proses selektif: lebih mengandalkan “deposit di sini, bukan di sana” dan “etsa ini, bukan itu,” menaikkan standar selektivitas dan kontrol cacat.

- Kompleksitas material: film, liner, dan lapisan barrier yang lebih eksotik yang harus seragam, rendah cacat, dan kompatibel dengan langkah downstream.

- Ekspektasi kecepatan ramp: transisi node dinilai bukan hanya oleh kapabilitas, tetapi seberapa cepat yield stabil pada volume.

Daftar periksa cepat untuk pembaca non-teknis

Saat membandingkan vendor alat atau pendekatan fab (termasuk Lam Research dan pesaing), fokuskan pada hasil:

- Peningkatan yield: Apakah proses mengurangi cacat pembunuh pada skala?

- Kontrol variabilitas: Seberapa ketat hasil dalam-wafer dan wafer-ke-wafer?

- Kecepatan ramp: Seberapa cepat node baru bisa mencapai produksi volume stabil?

- Reproduksibilitas dan uptime: Apakah alat tetap konsisten selama run panjang dengan downtime minimal?

Untuk menggali lebih jauh, jelajahi penjelasan terkait di /blog. Jika Anda sedang mengevaluasi opsi—atau membangun tooling internal untuk menganalisis yield, ekshursi, dan metrik ramp—lihat /pricing untuk bagaimana kami memikirkan biaya, kecepatan, dan kapabilitas (termasuk kapan platform build-with-chat seperti Koder.ai dapat menggantikan pipeline perangkat lunak warisan yang lebih lambat).