2025年5月04日·1 分

Lam Researchとチップ製造における複利的優位性

堆積とエッチ装置が最先端チップをどのように形作るか、なぜプロセスノウハウが世代を重ねて蓄積されるのか、それが歩留まり、ノード、スケーリングに何を意味するのか。

堆積とエッチ装置が最先端チップをどのように形作るか、なぜプロセスノウハウが世代を重ねて蓄積されるのか、それが歩留まり、ノード、スケーリングに何を意味するのか。

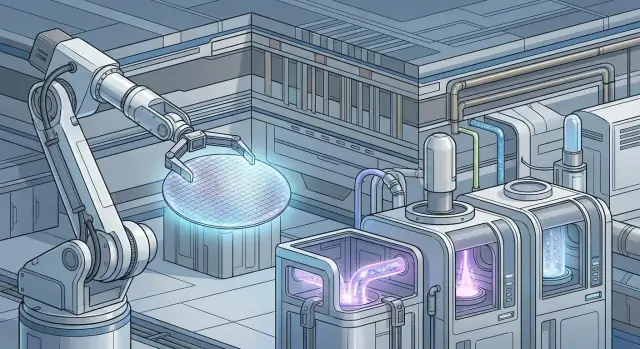

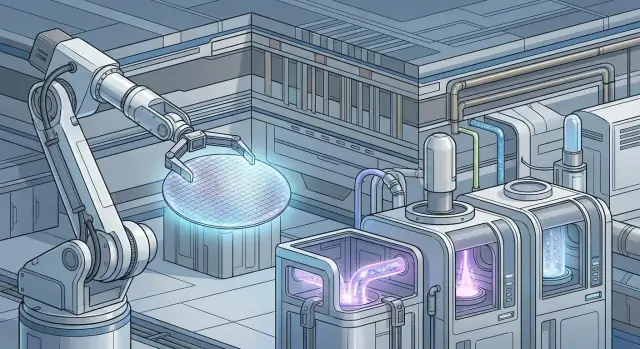

チップ製造を最も再現性のある動作までそぎ落とすと、何度も繰り返される二つの工程が浮かび上がります:**堆積(deposition)とエッチ(etch)**です。

堆積は「追加」の工程です。装置は超薄膜――導体、絶縁体、特別なバリア層――をウェーハ上に成膜し、場合によっては数原子分ずつ積み上げます。エッチは「除去」の工程です。装置は選択的に材料を削り取り、トランジスタや配線となる微細な特徴を作ります。理想的には下の層を傷つけずに行います。

チップがスケールダウンするにつれて、これら二つの工程はナノメートル領域で最も重要な調整ノブになりました:膜厚、形状、界面です。だからこそ、Lam Researchのような装置企業が最先端製造の中心に位置するのです。

「最先端」は一般に、最も進んだ高ボリューム生産ノードを指します――密度、消費電力、性能の目標が最も厳しく、誤差の余地が最小の領域です。単なるマーケティング数値ではなく、新しいデバイス構造や新材料が最初に現れる場所でもあります。

装置の性能(均一性、選択性、ダメージ制御、スループット)は重要ですが、**プロセスノウハウ(レシピ、統合の技、計測フィードバック、欠陥学習)**も同じくらい重要です。優れた装置を安定した高歩留まりの工場プロセスに変えるのはノウハウです。

この優位性は世代をまたいで複利的に積み上がります。各新ノードはゼロから始まるわけではなく、膜の成長、プラズマの挙動、微小なばらつきが大きな歩留まり変動を生む仕組みについての既存の学習に基づいて構築されるからです。

堆積とエッチのサイクルがなぜ繰り返し必要とされるかを理解するために、次を見ていきます:

現代のチップは単にシリコンの塊を「削り出す」わけではありません。むしろ微視的な層ケーキのように組み立てられ、超薄膜を何度も追加・パターニング・選択的除去していきます。それを何百回も繰り返すと、トランジスタや配線、絶縁バリアが積層され、3Dで絡み合った構造になります。

高レベルでは、チップ製造は次のリズムを繰り返します:

各ループが最終デバイスの1つの「スライス」を作ります――ゲート構造、コンタクトホール、配線など。これを積み重ねることで論理回路やメモリが現れます。

特徴が一桁ナノメートルで測られるとき、膜厚や形状の制御は「あったら良い」ものではありません。膜がわずかに厚すぎると狭い開口が塞がり、エッチが少し強すぎると線幅が広がったり下の層を傷つけたりします。側壁角、コーナーの丸み、表面粗さといった小さなプロファイル変化が電流の流れ方を変えてしまいます。

製造はプロセスステップ(特定の堆積/エッチ操作)に組織化され、それらはプロセスウィンドウ内で動作する必要があります――結果が一貫して許容範囲に入る設定範囲です。チップが高密度化するとそのウィンドウは狭くなります。そして後工程が前工程に依存するため、小さな逸脱がミスアライメント、短絡、開放につながり、最終的に歩留まりを下げます。

堆積はチップ製造の「追加」側です:超薄膜をウェーハ上に作り、後の工程でパターン化、防護、あるいは電気的分離を行えるようにします。これらの膜は装飾ではなく、各々が特定の役割を持ち、数十億の微細構造に渡って確実に機能しなければなりません。

**化学気相成長(CVD)**は反応性ガスを使ってウェーハ表面に固体膜を成長させます。広い領域を効率良く、良好な均一性で覆えるため、誘電体や一部の導電層に広く使われます。

**物理蒸着(PVD、しばしばスパッタリング)**はターゲット材料から原子を弾き出してウェーハに堆積させます。金属やハードマスク材料に一般的ですが、非常に深く狭い構造の側壁をコートするのは苦手なことがあります。

**原子層堆積(ALD)**は自己制限的な表面反応で分子単位の「投与」を繰り返して膜を作ります。速度は遅いですが、制御性と被覆性が重要な、特に最もタイトな3Dフィーチャで優れた性能を発揮します。

フィン、トレンチ、垂直ホールが登場すると、堆積は単純に「上面を塗る」問題ではなくなります。コンフォーマリティはフィーチャの上面、側壁、底面をどれだけ均一に覆うかを示します。

側壁が薄かったり、開口部でピンチオフが起きると電気的リーク、充填不良、下流エッチの失敗を招きます。深く狭いフィーチャでは高いコンフォーマリティが不可欠です。

厚さが正しくても、膜は次の実務要件を満たす必要があります:

最先端では、堆積は単なる「膜を足すこと」ではなく、後工程のエッチやパターン動作が予測可能に進むようにチューニングされた精密な材料工学です。

エッチはチップ製造の「除去」側です:膜を堆積してパターニングした後、露出した材料を除去してパターンを下の層に転写します。ここでの難しさは、ほとんどの場合「全部を除去したい」わけではなく、ある特定の材料だけを速く除去して別の層で止めたい点です。この性質が**選択比(セレクティビティ)**と呼ばれ、最先端ファブがエッチプロセスノウハウに大きく投資する理由です。

現代の積層はシリコン、シリコン酸化物、シリコン窒化物、金属、ハードマスクなど複数の材料を含みます。エッチ中に一層をきれいに除去しつつ「エッチストップ」層を残す必要があります。選択比が低いと重要な層が薄くなり、トランジスタ寸法が変わったり、リークが発生して歩留まりが落ちます。

高度なエッチの多くはプラズマを使います:低圧ガスをエネルギー化して反応性種を作る方法です。

同時に二つのことが起きます:

この二つのバランスを取るのが技術者の腕の見せ所です。化学が強すぎればアンダーカット(横方向の削れ)が起き、イオンエネルギーが強すぎれば保持すべき層を損傷します。

プロセスチームは通常、次の結果を追い求めます:

レシピが「正しい」場合でも、実際のウェーハは以下のように抵抗します:

最先端ノードでは、これらの細部を管理することがラボ実験と量産の差になります。

チップスケーリングを想像するとき、人はしばしば単一の画期的な露光機が線幅を小さくすると考えがちですが、実際のパターン転写はレジスト、ハードマスク、エッチの選択比、膜応力、クリーニングなど連鎖全体に制約されます。

フォトレジストはパターンを取るのに優れますが、深い精密エッチを耐えるには薄く脆弱です。そこでハードマスクスタックを積み上げます。

簡略化したフローは次の通りです:

各膜は単にその材質によって選ばれるのではなく、次のエッチでどう振る舞うか――どれだけ速く/遅くエッチされるか、どの程度粗さを作るか、形状をどれだけ保持するか――を基に選択されます。

重要寸法が単一のリソグラフィで確実に定義できなくなると、ファブはマルチパターニングを使います。それは単に露光工程が増えるだけでなく、スペーサー、マンドレル、トリム、カットマスクといった補助工程のために堆積/エッチループが増えることを意味します。

要点:最先端チップの「パターン」は、しばしば数回の堆積とエッチのサイクルの結果です。

各工程が次の開始条件を変えるため、最良の結果は材料、プラズマ条件、チャンバーの清浄度、洗浄工程を一つのシステムとしてチューニングした場合に出ます。あるエッチの小さな改善が次の堆積で消される(または増幅される)ことがあり、これがプロセス統合ノウハウの価値を世代を追って高めます。

平面トランジスタは比較的「平坦」でしたが、スケーリングにより業界は3Dへ移行しました:まずFinFET(ゲートがフィンを包む構造)、そして現在はゲートがチャネルを完全に包むGAA(ゲート・オール・アラウンド)や積層ナノシートなどが登場しています。

側壁、角、深い空洞があると、堆積はもはや「上面を塗る」だけでは済みません。膜はコンフォーマルである必要があり、トレンチ底部と上面でほぼ同じ厚さであることが求められます。

そのため、ALDや精密に調整されたCVDが最先端でより重要になります:側壁で数原子薄くなるだけでも抵抗が上がったり信頼性が落ちたり、バリアが弱くなって望ましくない拡散が起きます。

エッチは適切なプロファイルを作る必要があります:壁が直立していること、底部がきれいであること、粗さが最小であること、そして一つの材料を除去して別の材料を残す選択性を維持すること。密な3Dパターンでは、小さなオーバーエッチでも重要領域を傷つけ、アンダーエッチは残渣となって後工程の堆積を妨げます。

多くの現代構造は高アスペクト比で、深さに対して非常に狭いです。数十億のこのようなフィーチャで均一な結果を得るのは難しく、反応物、イオン、副生成物の移動が均一でないためにマイクロローディングや側壁損傷が発生しやすくなります。

GAAや高度な配線はより複雑な材料スタックと超薄界面をもたらします。これにより表面準備(プレクリーニング、穏やかなプラズマ処理、次の堆積前の界面制御)の要件が上がります。表面が数原子層しかない場合、プロセスノウハウがデバイスが動作するか否かの分かれ目になります。

「歩留まり」とはウェーハ上で正常に動作するダイの割合です。ウェーハに何千個ものダイが載っている場合、欠陥率のわずかな変化が販売可能な部品数を数百個分左右します。だから製造現場は小さな数値にまで執着します――大規模では小さな改善が大きな成果になります。

多くの歩留まり損失は顕微鏡で劇的に見えるものではなく、電気的な不良として現れます。一般的事例:

堆積やエッチの工程はこれらすべてに影響します。膜の厚さや組成、均一性が微妙に外れるだけでも、高度にスケールしたデバイスでは速度や消費電力の目標に届かなくなることがあります。

明らかな欠陥がなくても、ウェーハ内やウェーハ間のばらつきはデバイスの動作を一貫性のないものにします。片隅は高温になり、別の片隅は遅くなると製品のビニングが変わったり、最悪の場合部品が不合格になります。堆積率、プラズマ条件、エッチ選択比の厳密な制御がこれらの振れを減らします。

現代のファブは直感でプロセスを調整しません。メトロロジー(膜厚、重要寸法、プロファイル形状、均一性の測定)と検査(粒子やパターン欠陥の検出)があり、その結果がプロセス調整にフィードバックされます:

実務では、これがソフトウェア課題も生みます:ツール、メトロロジー、検査からのデータを縫い合わせてエンジニアが迅速に行動できる形にすることが必要です。チームは内部ダッシュボードやアラート、"何が変わったか"を追うツールを作り、信号から修正までのループを短くします。Koder.aiのようなプラットフォームは、プロセスとデータチームがチャットから軽量なウェブアプリを立ち上げ、歩留まりKPIや逸脱ノート、ラン履歴を統合するのに役立ちます。

最も価値あるノウハウは蓄積的です:各ノードがどの欠陥を引き起こすか、どの設定が時間とともにずれるか、どの組み合わせが安定かを教えます。これらの教訓は次のノードのプレイブックになり、空白の状態から始める必要を減らします。

堆積やエッチ装置は単一の「設定」で動くわけではなく、レシピで動きます。レシピは工程が時間軸でどう進むかを定義する構造化された手順群です。複数のフェーズ(安定化、前処理、メインステップ、後処理)を含み、それぞれにガス流量、圧力、温度、RF出力、タイミング、エンドポイントロジックがあります。パージ時間、ウェーハ取り扱い、チャンバー準備といった「静かな」詳細も含まれます。

ノードが進むにつれて、新材料や新しい3D形状が同時に導入されることが多く、平坦表面で機能していた膜が深く狭いフィーチャ上では異なる振る舞いをすることがあります。前世代で十分だった選択比が、新しいライナーやバリアを損傷し始めることもあります。

そのためレシピは進化します:デバイス目標(速度、消費電力、信頼性)が変わり、形状はタイトになり、統合制約が増えるからです。プロセス開発はチューニング→計測→再チューニングの長期サイクルであり、多くの場合数千ウェーハ後に初めて現れる問題を解く作業が含まれます。

量産では、一つのチャンバーが一度だけ良い結果を出せれば良いというわけではありません。再現性とは同じレシピがウェーハごとに同じ結果を出し続けることです。ツール間マッチングとは別の装置や別のファブにレシピを移しても同じ膜厚、プロファイル、均一性を厳密に満たすことを意味します。これができないと生産計画や歩留まりに悪影響を及ぼします。

コンタミネーション制御もこの現実の一部です。チャンバー内部表面に膜が堆積してくるとプラズマ条件や粒子リスクに影響を与えます。ファブはチャンバーコンディショニング、シーズニングラン、クリーニング、予防保守スケジュールを駆使してプロセスを安定させます。これらの運用ノウハウ――レシピを短時間ではなく数か月間維持する方法――こそ経験が蓄積される部分です。

最先端のチップは装置を買って設置し「実行ボタン」を押すだけで作れるわけではありません。堆積とエッチはチップのレイアウト、材料スタック、信頼性目標と密接に結びつくため、装置を作る側とファブを運用する側は共に反復を重ねていきます。

チップ設計者は必要な構造(小さいコンタクト、高いビア、新しい金属スタックなど)を定義します。ファブ内のプロセス統合チームがそれを工程フロー(この層を堆積し、パターン化し、エッチし、洗浄する)に翻訳します。装置メーカー(Lam Researchなど)はその要件を実際のハードウェア上で量産可能なレシピへと変える手助けを行います。

この引き渡しはすぐにループになります:初期ランでプロファイルのドリフト、残渣、ラインエッジ粗さ、予期せぬダメージが明らかになり、そのフィードバックはプロセスフローと装置設定の両方へ戻ります。時にはチャンバー材料、プラズマ源、ガス供給といったハードウェアオプションまで変えることがあります。

最先端では、堆積やエッチを孤立して最適化することはできません。各工程が次の工程の開始条件を変えるからです。膜密度の小さな変化がエッチ速度を変え、より攻撃的なエッチが下流の堆積のコンフォーマリティを悪化させることがあります。協調最適化は以下を整合させます:

ファブは常にスループット対精度のバランスを取っています:高速化はばらつきを増やし得る一方、超厳密制御は時間当たりのウェーハ数を減らします。同様に選択比対ダメージの緊張も繰り返し現れます:ある材料を優先的に選択的にエッチするための条件は、粗さや欠陥を招くようなより厳しい条件を要求するかもしれません。

提供価値の重要な一部は継続的な統合サポートです――現場でのトラブルシューティング、チャンバー間の性能マッチング、逸脱の削減、歩留まりが動いたときの迅速な回復支援。高ボリューム生産では、このパートナーシップが装置の仕様書と同じくらい重要になることがあります。

堆積やエッチ装置は仕様書上は素晴らしく見えても、それが24/7で何千ウェーハに対して同じ結果を出さなければ実用に耐えません。量産では信頼性と稼働率は「あると良い」ものではなく、不可欠です。これらは工場が出荷できる良品ウェーハ数を直接左右します。

堆積とエッチはプロセス安定性に生死がかかっています。ガス流量、チャンバー圧力、プラズマ出力、温度の小さなドリフトでも膜厚、側壁角、ダメージレベルが変わり、動作するレシピが歩留まり低下に直結することがあります。

だからこそ、先進的な装置(Lam Researchのシステムを含む)は再現性の高いハードウェアに多大な投資をします:安定したRF供給、精密なマスフロー制御、熱管理、逸脱を早期に検出するセンサーなどです。

プロセスが完璧でも、装置が頻繁に停止すれば生産は滞ります。実際のファブ出力は次の要素で形作られます:

メンテナンスしやすく、部品供給の見通しが良い装置はより多くのチャンバーを稼働させ、より多くのロットを流せます。

高い稼働率はウェーハ当たりコストを下げます:アイドル作業者が減り、高価なクリーンルーム空間の利用率が上がり、手直し時間が減ります。さらに、安定した可用性は納期の予測可能性を高めます。ラボ実験から量産への拡大は装置に異なる負荷をかけるため、長時間稼働や高いウェーハスタート、厳しい欠陥予算が弱点を早期に露呈させます。したがって信頼性工学は「プロセス能力」の核心になります。

チップがより小さなノードやより多くの3D構造へ進むにつれて、進展は堆積とエッチの工程を極めて精密に何百回も繰り返す能力に依存します。次のボトルネックは単一のブレークスルーではなく、各サイクルを一貫して保ちつつ歩留まりとばらつきを管理し、新プロセスを需要に間に合わせる速さで立ち上げる累積的困難であることが多いです。

いくつかのトレンドが堆積/エッチに最大の負荷をかけるでしょう:

装置ベンダーやファブのアプローチ(Lam Researchや他社)を比較する際は、成果に注目してください:

より詳細を知りたい場合は /blog の関連解説をお読みください。ツールを比較したり歩留まり、逸脱、立ち上げメトリクスを解析する内部ツールを構築する場合は、/pricing を参照してください。Koder.ai のようなチャットと連携して構築するプラットフォームは、従来の遅いソフトウェア開発に代わる選択肢となり得ます。

堆積は**「足す」工程です:装置が超薄膜(金属、誘電体、バリア、ライナー、ハードマスクなど)をウェーハに形成します。エッチは「削る」**工程です:特定の材料を選択的に除去してパターンを転写し、素子や配線の形状を作ります。

スケーリングはナノメートル寸法での厚さ、形状、界面の制御に依存するため、堆積/エッチの品質は性能と歩留まりに直接影響します。

**「最先端」**は通常、ハイボリューム生産で最も進んだノードを指します。そこではデバイス構造や材料が新しく、許容誤差が非常に小さいためです。

マーケティング上の単なる数字ではなく、プロセスウィンドウが狭く、小さな変動に対する感度が高い領域を意味します。

現代のチップは繰り返しループで作られるからです:

特徴が小さく、積層が複雑になるほど、1つの「層」を狙い通りの寸法やプロファイルにするために複数の堆積–エッチ–クリーンのサイクルが必要になります。

コンフォーマリティ(均一被覆性)は、3D形状の上面、側壁、底面に膜がどれだけ均一に付くかを表します。

均一でない被覆は:

そのため、コンフォーマリティが重要な場合は**ALD(原子層堆積)**のような手法が多用されます。

**選択比(セレクティビティ)**は、ある材料を別の材料よりどれだけ速く除去できるかを示します(しばしばエッチストップ層を残す必要があります)。

高い選択比があれば:

フォトレジストはパターンを取るのに優れていますが、深く精密なエッチを耐えるには薄すぎたり脆弱なことが多いです。そこでファブはハードマスクスタックを構築します—標的層の上に堆積した、選択性や耐エッチ性を考慮した膜群です。

典型的な流れ:

ハードマスクの選択はエッチ耐性、選択比、プロファイル制御で決まります。

マルチパターニングは、単一のリソグラフィで最終ピッチを確実に定義できないときに、1つの密なパターンを複数の露光と転写に分割する手法です。

これにより、スペーサーやマンドレル形成などの補助工程が追加され、1つの最終的なフィーチャを作るために必要な堆積+エッチの回数(および洗浄やメトロロジー)が増えます。

高アスペクト比(深さに比べて幅が非常に小さい)では、輸送が難しくなります:

その結果、ノッチやフッティング、残渣、粗さ、ばらつきのリスクが高まり、プロセス調整がより厳格になります。

歩留まりはウェーハ上の正しく動作するダイの割合です。堆積やエッチは、電気的な不具合につながる欠陥やばらつきを生み出すことで歩留まりに影響します。一般的な事例:

ナノスケールでは厚さやプロファイルの小さな変化がデバイス特性をずらし、歩留まり低下を招くことがあります。

仕様だけではなく、実生産ではプロセスノウハウ(レシピ、統合順序、欠陥学習、ツール間マッチング)が差を生みます。

このノウハウが複利的に蓄積されるのは、各ノードが以下のような学びを次に引き継ぐためです:

そのため、Lam Researchのような装置メーカーが最先端製造で戦略的に重要になることがあります。