04 ਮਈ 2025·8 ਮਿੰਟ

Lam Research ਅਤੇ ਚਿਪ ਨਿਰਮਾਣ ਵਿੱਚ ਗੁਣਾ ਫਾਇਦਾ

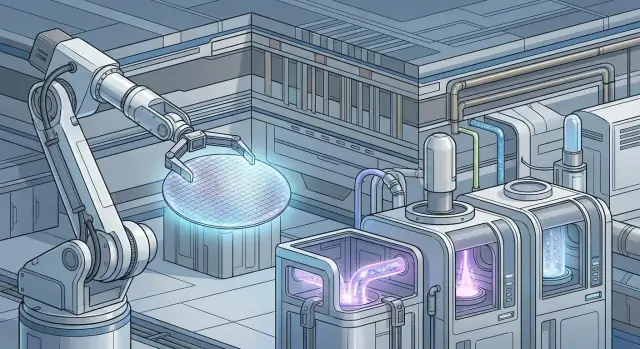

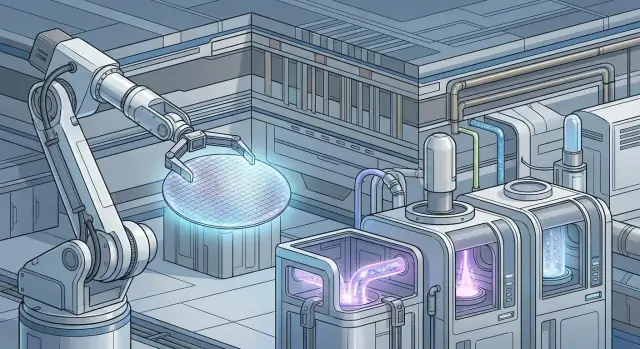

ਕਿਵੇਂ deposition ਅਤੇ etch ਟੂਲ ਅਗਲੇ ਪੱਧਰ ਦੇ ਚਿਪ ਤਿਆਰ ਕਰਦੇ ਹਨ, ਕਿਉਂ ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਆਪਣੇ ਆਪ 'ਤੇ ਸਮੇਂ ਦੇ ਨਾਲ ਗੁਣਾ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਇਸਦਾ yield, ਨੋਡ, ਅਤੇ ਸਕੇਲਿੰਗ 'ਤੇ ਕੀ ਅਰਥ ਹੁੰਦਾ ਹੈ।

ਕਿਵੇਂ deposition ਅਤੇ etch ਟੂਲ ਅਗਲੇ ਪੱਧਰ ਦੇ ਚਿਪ ਤਿਆਰ ਕਰਦੇ ਹਨ, ਕਿਉਂ ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਆਪਣੇ ਆਪ 'ਤੇ ਸਮੇਂ ਦੇ ਨਾਲ ਗੁਣਾ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਇਸਦਾ yield, ਨੋਡ, ਅਤੇ ਸਕੇਲਿੰਗ 'ਤੇ ਕੀ ਅਰਥ ਹੁੰਦਾ ਹੈ।

ਜੇ ਤੁਸੀਂ ਚਿਪ ਨਿਰਮਾਣ ਨੂੰ ਉਸਦੀ ਸਭ ਤੋਂ ਦੁਹਰਾਏ ਜਾਣ ਵਾਲੀਆਂ ਗਤਿਵਿਧੀਆਂ ਤੱਕ ਘਟਾ ਦਿਓ, ਤਾਂ ਦੋ ਕਦਮ ਵਾਰ-ਵਾਰ ਉभर ਕੇ ਆਉਂਦੇ ਹਨ: deposition ਅਤੇ etch।

Deposition "ਜੋੜਨ" ਕਦਮ ਹੈ। ਟੂਲ ਵਾਫਰ 'ਤੇ ਬਹੁਤ ਪਤਲੀ ਫਿਲਮਾਂ ਰੱਖਦੇ ਹਨ—ਚਾਲਕ, ਇਨਸੂਲੇਟਰ, ਜਾਂ ਖਾਸ ਬੈਰਿਅਰ ਲੇਅਰ—ਕਈ ਵਾਰੀ ਕੁਝ ਐਟਮਾਂ ਦੀ ਮਾਤਰਾ ਵੱਜੋਂ। Etch "ਹਟਾਉਣ" ਕਦਮ ਹੈ। ਟੂਲ ਚੁਣੀਂਦਾ ਤੌਰ 'ਤੇ ਸਮੱਗਰੀ ਨੂੰ ਕੱਦਦੇ ਹਨ ਤਾਂ ਕਿ ਛੋਟੇ-ਛੋਟੇ ਫੀਚਰ ਬਣਨ ਜੋ ਟਰਾਂਜ਼ਿਸਟਰ ਅਤੇ ਵਾਇਰਿੰਗ ਬਣਾਉਂਦੇ ਹਨ, ਆਦੇਸ਼ਕ ਤੌਰ 'ਤੇ ਹੇਠਾਂ ਵਾਲੀਆਂ ਪਰਤਾਂ ਨੂੰ ਨੁਕਸਾਨ ਨਹੀਂ ਪਹੁੰਚਾਉਂਦੇ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਚਿਪ ਸਕੇਲ ਹੋਏ ਹਨ, ਇਹ ਦੋ ਕਦਮ ਨੈਨੋਮੀਟਰ ਪੈਮਾਨਿਆਂ 'ਤੇ ਸਭ ਤੋਂ ਮਹੱਤਵਪੂਰਨ ਨਿਯੰਤਰਕ ਬਣ ਗਏ ਹਨ: ਮੋਟਾਈ, ਆਕਾਰ, ਅਤੇ ਇੰਟਰਫੇਸ। ਇਸੀ ਲਈ ਉਪਕਰਨ ਕੰਪਨੀਆਂ ਜਿਵੇਂ Lam Research ਅੱਗੇ-ਪੰਛਲੇ ਨਿਰਮਾਣ ਦੇ ਦਿਲ ਦੇ ਨੇੜੇ ਬੈਠਦੀਆਂ ਹਨ।

“Leading-edge” ਆਮ ਤੌਰ 'ਤੇ ਸਭ ਤੋਂ ਅਡਵਾਂਸਡ, ਹਾਈ-ਵਾਲੀਅਮ ਉਤਪਾਦਨ ਨੋਡਾਂ ਨੂੰ ਦਰਸਾਉਂਦਾ ਹੈ—ਜਿੱਥੇ ਡੈਨਸਿਟੀ, ਪਾਵਰ, ਅਤੇ ਪ੍ਰਦਰਸ਼ਨ ਲਕਸ਼ਾਂ ਸਭ ਤੋਂ ਜ਼ਿਆਦਾ ਤੇਜ਼ ਹੁੰਦੇ ਹਨ, ਅਤੇ ਗਲਤੀ ਲਈ ਮਾਰਜਿਨ ਸਭ ਤੋਂ ਘੱਟ। ਇਹ ਸਿਰਫ਼ ਮਾਰਕੀਟਿੰਗ ਨੰਬਰ ਨਹੀਂ; ਇਹ ਓਹੀ ਥਾਂ ਹੈ ਜਿੱਥੇ ਨਵੇਂ ਡਿਵਾਈਸ ਸਟ੍ਰਕਚਰ ਅਤੇ ਨਵੀਆਂ ਸਮੱਗਰੀ ਪਹਿਲਾਂ ਆਉਂਦੀਆਂ ਹਨ।

ਟੂਲ ਦੀ ਸਮਰੱਥਾ ਮਾਇਨੇ ਰੱਖਦੀ ਹੈ (ਯੂਨੀਫਾਰਮਿਟੀ, ਸੈਲੇਕਟਿਵਿਟੀ, ਨੁਕਸਾਨ ਕੰਟਰੋਲ, throughput)। ਪਰ ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਵੀ ਬੜੀ ਅਹਮ ਹੈ: ਰੈਸੀਪੀ, ਇੰਟਿਗ੍ਰੇਸ਼ਨ ਚਾਲਾਕੀਆਂ, ਮੈਟਰੋਲੋਜੀ ਪ੍ਰਤੀਕ੍ਰਿਆ, ਅਤੇ ਡਿਫੈਕਟ-ਸਿੱਖਣ ਜੋ ਵਧੀਆ ਟੂਲ ਨੂੰ ਸਥਿਰ, ਉੱਚ-yield ਫੈਕਟਰੀ ਪ੍ਰੋਸੈਸ ਵਿੱਚ ਬਦਲ ਦਿੰਦੇ ਹਨ।

ਇਹ ਫਾਇਦਾ ਤਕਨਾਲੋਜੀ ਜਨਰੇਸ਼ਨਾਂ 'ਤੇ ਕੁਝ ਇਸ ਤਰ੍ਹਾਂ ਘਟਦਾ ਹੈ ਕਿ ਹਰ ਨਵਾਂ ਨੋਡ ਜ਼ੀਰੋ ਤੋਂ ਸ਼ੁਰੂ ਨਹੀਂ ਹੁੰਦਾ—ਇਹ ਪਿਛਲੀ ਸਿੱਖਿਆ 'ਤੇ ਬਣਦਾ ਹੈ ਕਿ ਫਿਲਮ ਕਿਵੇਂ ਵਧਦੀਆਂ ਹਨ, ਪਲਾਜ਼ਮਾ ਕਿਵੇਂ ਵਰਤੋਂ ਕਰਦੇ ਹਨ, ਅਤੇ ਛੋਟੀ ਵੈਰੀਏਸ਼ਨਾਂ ਨਾਲ yield 'ਚ ਵੱਡੇ ਝਟਕੇ ਕਿਵੇਂ ਆਉਂਦੇ ਹਨ।

ਇਹ ਸਮਝਣ ਲਈ ਕਿ deposition ਅਤੇ etch ਚੱਕਰ ਕਿਉਂ ਗੁਣਾਂਕਿਤ ਹੋ ਰਹੇ ਹਨ, ਅਸੀਂ ਦੇਖਾਂਗੇ:

ਇੱਕ ਆਧੁਨਿਕ ਚਿਪ ਕਿਸੇ ਸਿਲਿਕਾਨ ਦੇ ਬਲਾਕ ਤੋਂ "ਮਸ਼ੀਨ" ਨਹੀਂ ਬਣਾਈ ਜਾਂਦੀ। ਇਹ ਉਸਤਾਂ 'ਤੇ ਬਣਾਈ ਜਾਂਦੀ ਹੈ—ਬਹੁਤ ਹੀ ਨਿੱਕੀ ਲੇਅਰਾਂ ਨੂੰ ਮੁੜ-ਮੁੜ ਜੋੜ ਕੇ, ਪੈਟਰਨ ਕਰਕੇ, ਅਤੇ ਜੇੜੀ ਚੀਜ਼ ਨਹੀਂ ਚਾਹੀਦੀ ਉਸਨੂੰ ਹਟਾ ਕੇ। ਇਹ ਕੰਮ ਸੈਂਕੜੇ ਵਾਰੀ ਕਰੋ, ਅਤੇ ਤੁਸੀਂ ਟਰਾਂਜ਼ਿਸਟਰ, ਵਾਇਰਿੰਗ, ਅਤੇ ਇਨਸੂਲੇਟਿੰਗ ਬੈਰਿਅਰ ਨੂੰ 3D ਵਿੱਚ ਸਟਾਕ ਕੀਤੇ ਹੋਏ ਵੇਖੋਂਗੇ।

ਉੱਚ ਸਤਰ 'ਤੇ, ਚਿਪ ਨਿਰਮਾਣ ਇੱਕ ਪਰਿਚਿਤ ਰਿਦਮ ਦੁਆਰਾ ਚੱਲਦਾ ਹੈ:

ਹਰ ਲੂਪ ਆਖਰੀ ਡਿਵਾਈਸ ਦੀ ਇੱਕ "ਸਲਾਇਸ" ਬਣਾਉਂਦਾ ਹੈ—ਗੇਟ ਸਟ੍ਰਕਚਰ, ਕਾਂਟੈਕਟ ਹੋਲ, ਜਾਂ ਇੰਟਰਕਨੈਕਟ ਲਾਈਨ—ਜਦ ਤੱਕ ਲੋਜਿਕ ਅਤੇ ਮੈਮੋਰੀ ਸਟੈਕ ਤੋਂ ਉਭਰ ਕੇ ਆਉਂਦੇ ਹਨ।

ਜਦ ਫੀਚਰ ਇਕੱਲੇ-ਅੰਕ ਨੈਨੋਮੀਟਰਾਂ ਵਿੱਚ ਮਾਪੇ ਜਾਂਦੇ ਹਨ, ਮੋਟਾਈ ਅਤੇ ਆਕਾਰ ਕੰਟਰੋਲ "ਚੰਗੀ ਗੱਲ" ਰਹਿ ਕੇ ਨਹੀਂ ਰਹਿੰਦੇ। ਇੱਕ ਫਿਲਮ ਜੋ ਥੋੜ੍ਹੀ ਜ਼ਿਆਦਾ ਮੋਟੀ ਹੋਵੇ ਤਾਂ ਇੱਕ ਤੰਗ ਚਾਨਣ ਨੂੰ ਬੰਦ ਕਰ ਸਕਦੀ ਹੈ; ਇੱਕ ਐਗਰੈਸੀਵ etch ਇੱਕ ਲਾਈਨ ਨੂੰ ਵਿਆਪਕ ਕਰ ਸਕਦੀ ਹੈ ਜਾਂ ਹੇਠਾਂ ਵਾਲੀ ਪਰਤ ਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾ ਸਕਦੀ ਹੈ। ਛੋਟੇ ਪ੍ਰੋਫਾਈਲ ਬਦਲਾਅ—ਸਾਈਡਵਾਲ ਐਂਗਲ, ਕੋਨਰ ਰਾਊਂਡਿੰਗ, ਸਤਹ ਰਫ਼ਨੈਸ—ਬਿਜਲੀ ਦੇ ਪ੍ਰਵਾਹ ਨੂੰ ਬਦਲ ਸਕਦੇ ਹਨ।

ਨਿਰਮਾਣ ਨੂੰ ਪ੍ਰੋਸੈਸ ਸਟੈਪ (ਖਾਸ deposition/etch ਓਪਰੇਸ਼ਨ) 'ਚ ਸੰਗਠਿਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ ਜੋ ਇੱਕ ਪ੍ਰੋਸੈਸ ਵਿੰਡੋ ਦੇ ਅੰਦਰ ਚਲਣੇ ਚਾਹੀਦੇ ਹਨ—ਉਹ ਰੇਂਜ ਜਿਸ ਵਿੱਚ ਨਤੀਜਿਆਂ ਨੂੰ ਨਿਰੰਤਰ ਤੌਰ 'ਤੇ ਕਬੂਲਯੋਗ ਮਿਲਦਾ ਹੈ। ਜਿਵੇਂ-ਜਿਵੇਂ ਚਿਪ ਘਣੇ ਹੋ ਰਹੇ ਹਨ, ਉਹ ਵਿੰਡੋ ਛੋਟੇ ਹੁੰਦੇ ਜਾਂਦੇ ਹਨ। ਅਤੇ ਕਿਉਂਕਿ ਆਖਰੀ ਪਰਤਾਂ ਪਹਿਲਾਂ ਵਾਲਿਆਂ 'ਤੇ ਨਿਰਭਰ ਹੁੰਦੀਆਂ ਹਨ, ਇੱਕ ਛੋਟੀ ਗਲਤੀ cascade ਕਰ ਕੇ ਮਿਸਅਲਾਇਨਮੈਂਟ, ਸ਼ੋਰਟ, ਓਪਨ, ਅਤੇ ਅਖੀਰਕਾਰ ਘੱਟ yield 'ਤੇ ਲੈ ਆ ਸਕਦੀ ਹੈ।

Deposition ਚਿਪ ਨਿਰਮਾਣ ਦਾ "ਸਮੱਗਰੀ ਜੋੜਨ" ਹਿਸਾ ਹੈ: ਵਾਫਰ 'ਤੇ ਬਹੁਤ ਪਤਲੀ ਫਿਲਮ ਬਣਾਉਣਾ ਤਾਂ ਜੋ ਅਗਲੇ ਕਦਮ ਉਨ੍ਹਾਂ ਨੂੰ ਪੈਟਰਨ, ਸੁਰੱਖਿਆ, ਜਾਂ ਬਿਜਲੀਕ ਤੌਰ 'ਤੇ ਅਲੱਗ ਕਰਨ ਲਈ ਵਰਤ ਸਕਣ। ਇਹ ਫਿਲਮਾਂ ਸਜਾਵਟੀ ਨਹੀਂ—ਹਰ ਇਕ ਨੂੰ ਖਾਸ ਕੰਮ ਲਈ ਚੁਣਿਆ ਜਾਂਦਾ ਹੈ, ਅਤੇ ਇਹਨਾਂ ਨੂੰ ਬਿਲਕੁਲ ਕੁਝ ਅਟਮਾਂ ਤੋਂ ਮਿਲੀਅਰਾਂ ਫੀਚਰਾਂ ਤੱਕ ਭਰੋਸੇਯੋਗ ਹੋਣਾ ਚਾਹੀਦਾ ਹੈ।

Chemical Vapor Deposition (CVD) ਰੀਏਕਟੀਵ ਗੈਸਾਂ ਵਰਤਦਾ ਹੈ ਜੋ ਵਾਫਰ ਸਤਹ 'ਤੇ ਠੋਠੀ ਫਿਲਮ ਬਣਾਉਂਦੀਆਂ ਹਨ। ਇਹ ਕਈ ਡਾਇਐਲੈਕਟ੍ਰਿਕ ਅਤੇ ਕੁਝ ਚਾਲਕ ਪਰਤਾਂ ਲਈ ਵਿਆਪਕ ਤੌਰ 'ਤੇ ਵਰਤਿਆ ਜਾਂਦਾ ਹੈ ਕਿਉਂਕਿ ਇਹ ਵੱਡੀਆਂ ਸਥਲਾਂ ਨੂੰ ਪ੍ਰਭਾਵਸ਼ਾਲੀ ਅਤੇ ਚੰਗੀ ਯੂਨੀਫਾਰਮਿਟੀ ਨਾਲ ਕਵਰ ਕਰ ਸਕਦਾ ਹੈ।

Physical Vapor Deposition (PVD) (ਅਕਸਰ "sputtering") ਹੇਠਾਂ ਦੇ ਲਕੜੀ ਨੂੰ ਝਟਕ ਕੇ ਐਟਮਾਂ ਨੂੰ ਵਾਫਰ 'ਤੇ ਰੱਖਦਾ ਹੈ। PVD ਧਾਤਾਂ ਅਤੇ ਹਾਰਡਮਾਸਕ ਸਮੱਗਰੀ ਲਈ ਆਮ ਹੈ, ਖਾਸ ਕਰਕੇ ਜਦ ਤੁਸੀਂ ਇੱਕ ਘਣੀ ਫਿਲਮ ਚਾਹੁੰਦੇ ਹੋ—ਪਰ ਇਹ ਬਹੁਤ ਡੂੰਘੀਆਂ, ਤੰਗ ਸਟ੍ਰਕਚਰਾਂ ਦੀ ਸਾਈਡਵਾਲਾਂ ਨੂੰ ਕੋਟ ਕਰਨ ਵਿਚ ਮੁਸ਼ਕਲ ਕਰ ਸਕਦਾ ਹੈ।

Atomic Layer Deposition (ALD) ਹਰ ਇਕ ਮੌਲੀਕਿਊਲਰ "ਡੋਜ਼" ਨੂੰ ਸਵੈ-ਸੀਮਤ ਸਤਹ ਪ੍ਰਤੀਕ੍ਰਿਆਵਾਂ ਰਾਹੀਂ ਜਮਾਉਂਦਾ ਹੈ। ਇਹ ਧੀਮਾ ਹੁੰਦਾ ਹੈ, ਪਰ ਜਦ ਨਿਯੰਤਰਣ ਅਤੇ ਕਵਰੇਜ ਸਪੀਡ ਤੋਂ ਜ਼ਿਆਦਾ ਮਹੱਤਵਪੂਰਨ ਹੋਵੇ—ਖਾਸ ਕਰਕੇ ਸਭ ਤੋਂ ਤੰਗ 3D ਫੀਚਰਾਂ ਵਿੱਚ—ਇਹ ਬਹੁਤ ਅਸਰਦਾਰ ਹੁੰਦਾ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਚਿਪ ਫਿਨ, ਟ੍ਰੈਨਚ, ਅਤੇ ਵਰਟਿਕਲ ਹੋਲ ਵੱਲ ਵਧੇ, deposition ਸਿਰਫ਼ "ਉੱਪਰ ਨੂੰ ਰੰਗਨ" ਦਾ ਮੁੱਦਾ ਨਹੀਂ ਰਿਹਾ। Conformality ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਫਿਲਮ ਟੌਪ ਸਤਹ, ਸਾਈਡਵਾਲ, ਅਤੇ ਤਲ ਨੂੰ ਕਿੰਨੀ ਸਮਾਨ ਤਰ੍ਹਾਂ ਕੋਟ ਕਰਦੀ ਹੈ।

ਜੇ ਕੋਈ ਪਰਤ ਸਾਈਡਵਾਲ 'ਤੇ ਪਤਲੀ ਹੋਵੇ ਜਾਂ ਖੋਲ੍ਹੇ 'ਤੇ ਪਿੰਚ ਆ ਜਾਵੇ, ਤਾਂ ਬਿਜਲੀਕ ਰੀਕਲਾਜ਼, ਖਰਾਬ ਭਰਾਈ, ਜਾਂ ਬਾਅਦ ਦੇ etch ਕਦਮਾਂ 'ਚ ਫੇਲਿਊਰ ਹੋ ਸਕਦੇ ਹਨ। ਡੂੰਘੇ, ਤੰਗ ਫੀਚਰਾਂ ਲਈ ਉੱਚੀ conformality ਬਹੁਤ ਜ਼ਰੂਰੀ ਹੈ।

ਭਾਵੇਂ ਮੋਟਾਈ ਸਹੀ ਹੋਵੇ, ਫਿਲਮ ਨੂੰ ਕੁਝ ਪ੍ਰਯੋਗਿਕ ਮਾਪਦੰਡ ਪੂਰੇ ਕਰਨੇ ਪੈਦੈ ਹਨ:

Leading-edge 'ਤੇ deposition ਸਿਰਫ਼ "ਫਿਲਮ ਜੋੜਣਾ" ਨਹੀਂ; ਇਹ ਸੁਖਦ ਅਤੇ ਅਗਲੇ etch ਅਤੇ pattern ਕਦਮਾਂ ਨੂੰ ਭਰੋਸੇਯੋਗ ਬਣਾਉਣ ਲਈ ਸੁੰਝੀਵਾਨ ਮੈਟਿਰੀਅਲ ਇੰਜੀਨੀਅਰਿੰਗ ਹੈ।

Etch ਚਿਪ ਨਿਰਮਾਣ ਦਾ "ਘਟਾਉਣ ਵਾਲਾ" ਹਿੱਸਾ ਹੈ: ਇੱਕ ਫਿਲਮ ਡਿਪੋਜ਼ਿਟ ਅਤੇ resist ਨਾਲ ਪੈਟਰਨ ਹੋਣ ਤੋਂ ਬਾਅਦ, etch ਉਹ ਖੁੱਲ੍ਹੇ ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਂਦਾ ਹੈ ਤਾਂ ਕਿ ਪੈਟਰਨ ਹੇਠਾਂ ਵਾਲੀ ਪਰਤ ਵਿੱਚ ਟਰਾਂਸਫਰ ਹੋ ਜਾਵੇ। ਚਾਲਾਕੀ ਇਹ ਹੈ ਕਿ ਤੁਸੀਂ ਅਕਸਰ ਸਭ ਕੁਝ ਹਟਾਉਣਾ ਨਹੀਂ ਚਾਹੁੰਦੇ—ਤੁਸੀਂ ਇੱਕ ਖਾਸ ਸਮੱਗਰੀ ਨੂੰ ਤੇਜ਼ੀ ਨਾਲ ਹਟਾਉਣਾ ਚਾਹੁੰਦੇ ਹੋ ਅਤੇ ਦੂਜੀ 'ਤੇ ਰੁਕਣਾ ਚਾਹੁੰਦੇ ਹੋ। ਇਹ ਗੁਣ selectivity कहलਾਂਦੀ ਹੈ, ਅਤੇ ਇਹੀ ਕਾਰਨ ਹੈ ਕਿ leading-edge ਫੈਬ etch ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਵਿੱਚ ਇਨੇ ਨਿਵੇਸ਼ ਕਰਦੇ ਹਨ (ਅਤੇ Lam Research ਵਰਗੇ ਟੂਲ ਵੇਂਡਰ ਇਸਨੂੰ ਸੁਧਾਰਨ ਵਿੱਚ ਸਾਲ ਲਗਾਉਂਦੇ ਹਨ)।

ਆਧੁਨਿਕ ਸਟੈਕ ਵਿੱਚ ਸਿਲਿਕਾਨ, ਸਿਲਿਕਾਨ ਆਕਸਾਈਡ, ਸਿਲਿਕਾਨ ਨਾਈਟ੍ਰਾਈਡ, ਧਾਤਾਂ, ਅਤੇ ਹਾਰਡਮਾਸਕ ਸ਼ਾਮਲ ਹੋ ਸਕਦੇ ਹਨ। Etch ਦੌਰਾਨ ਤੁਸੀਂ ਇੱਕ ਪਰਤ ਨੂੰ ਸਾਫ਼ ਕਰਨੀ ਚਾਹੁੰਦੇ ਹੋ ਬਿਨਾਂ "etch stop" ਪਰਤ ਨੂੰ ਖਤਮ ਕੀਤੇ। ਖਰਾਬ selectivity ਮਹੱਤਵਪੂਰਨ ਪਰਤਾਂ ਨੂੰ ਪਤਲਾ ਕਰ ਸਕਦੀ ਹੈ, ਟਰਾਂਜ਼ਿਸਟਰ ਮਾਪ ਨੂੰ ਬਦਲ ਸਕਦੀ ਹੈ, ਜਾਂ ਲੀਕੇਜ ਰਾਹਾਂ ਬਣ ਸਕਦੇ ਹਨ ਜੋ yield ਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾਉਂਦੇ ਹਨ।

ਅਧਿਕ ਤਕਨੀਕੀ etching ਇੱਕ ਪਲਾਜ਼ਮਾ ਵਰਤਦਾ ਹੈ: ਇੱਕ ਨੀਚੇ-ਦਬਾਅ ਵਾਲੀ ਗੈਸ ਜਿਸਨੂੰ ਰੀਏਕਟਿਵ ਪ੍ਰਜਾਤੀਆਂ ਵਿੱਚ ਉਰਜਿਤ ਕੀਤਾ ਜਾਂਦਾ ਹੈ।

ਇੱਕ ਸਮੇਂ ਦੋ ਚੀਜ਼ਾਂ ਹੁੰਦੀਆਂ ਹਨ:

ਇਨ੍ਹਾਂ ਦਾ ਸੰਤੁਲਨ ਕਲਾ ਹੈ: ਬਹੁਤ ਜ਼ਿਆਦਾ ਰਸਾਇਣ ਫੀਚਰਾਂ ਨੂੰ ਅੰਡਰਕਟ ਕਰ ਸਕਦੀ ਹੈ; ਬਹੁਤ ਜ਼ਿਆਦਾ ਆਇਨ ਉਰਜਾ ਜੋ ਤੁਸੀਂ ਰੱਖਣਾ ਚਾਹੁੰਦੇ ਹੋ ਉਸਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾ ਸਕਦੀ ਹੈ।

ਪ੍ਰੋਸੈਸ ਟੀਮਾਂ ਆਮ ਤੌਰ 'ਤੇ ਕੁਝ ਨਤੀਜੇ ਪ੍ਰਾਪਤ ਕਰਨ ਦੀ ਕੋਸ਼ਿਸ਼ ਕਰਦੀਆਂ ਹਨ:

ਭਾਵੇਂ ਰੈਸੀਪੀ "ਸਹੀ" ਹੋਵੇ, ਅਸਲੀ ਵਾਫਰ ਮੁਸਕਿਲ ਕਰਦੇ ਹਨ:

Leading nodes 'ਤੇ, ਇਹ ਵਿਸਥਾਰਕ ਬਿੰਦੂ ਲੈਬ ਡੈਮੋ ਅਤੇ ਹਾਈ-ਵਾਲੀਅਮ ਨਿਰਮਾਣ ਵਿਚਕਾਰ ਫਰਕ ਹੁੰਦੇ ਹਨ।

ਜਦ ਲੋਕ ਚਿਪ ਸਕੇਲਿੰਗ ਦੀ ਸੋਚਦੇ ਹਨ, ਉਹ ਅਕਸਰ ਇੱਕ ਇਕਲ ਪ੍ਰਗਟਾਊ ਮਸ਼ੀਨ ਦੀ ਤਸਵੀਰ ਬਣਾਂਦੇ ਹਨ ਜੋ ਸਭ ਤੋਂ ਛੋਟੀ ਲਾਈਨਾਂ ਨੂੰ "ਪ੍ਰਿੰਟ" ਕਰਦੀ ਹੈ। ਅਸਲ ਵਿੱਚ, ਪੈਟਰਨ ਟਰਾਂਸਫਰ ਸਾਰੇ ਚੇਨ-ਰਿੰਗ ਤੋਂ ਪ੍ਰਭਾਵਿਤ ਹੁੰਦਾ ਹੈ—ਰਜ਼ਿਸਟ, ਹਾਰਡਮਾਸਕ, etch selectivity, ਫਿਲਮ ਸਟ੍ਰੈੱਸ, ਅਤੇ ਕਲੀਨ—ਨਾ ਕਿ ਕਿਸੇ ਇੱਕ ਜਾਦੂਈ ਟੂਲ ਤੋਂ।

Photoresist ਪੈਟਰਨ ਕੈਪਚਰ ਕਰਨ ਲਈ ਵਧੀਆ ਹੈ, ਪਰ ਆਮ ਤੌਰ 'ਤੇ ਇਹ ਬਹੁਤ ਪਤਲਾ ਅਤੇ ਨਾਜ਼ੁਕ ਹੁੰਦਾ ਹੈ ਤਾਂ ਜੋ ਆਧੁਨਿਕ ਡੂੰਘੇ, ਸਤਿਕਾਰ etch ਸਹਿਣ ਸਕੇ। ਇਸ ਲਈ ਫੈਬ ਹਾਰਡਮਾਸਕ ਸਟੈਕ ਬਣਾਉਂਦੇ ਹਨ—ਧਿਆਨ ਨਾਲ ਚੁਣੀਆਂ ਗਈਆਂ ਫਿਲਮਾਂ ਜੋ ਟਾਰਗਟ ਲੇਅਰ 'ਤੇ ਰੱਖੀਆਂ ਜਾਂਦੀਆਂ ਹਨ।

ਸਰਲ ਫਲੋ ਇਹ ਹੈ:

ਹਰ ਡਿਪੋਜ਼ਿਟ ਕੀਤੀ ਫਿਲਮ ਚੁਣੀ ਜਾਂਦੀ ਹੈ ਨਾ ਕਿ ਸਿਰਫ਼ ਉਸਦੀ ਕਿਸਮ ਲਈ, ਬਲਕਿ ਇਸ ਲਈ ਵੀ ਕਿ ਇਹ ਅਗਲੇ etch ਦੌਰਾਨ ਕਿਵੇਂ ਵਰਤੇਗੀ: ਇਹ ਕਿੰਨੀ ਤੇਜ਼ੀ ਨਾਲ etch ਹੁੰਦੀ ਹੈ, ਕਿੰਨਾ ਰਫ਼ਨੈਸ ਬਣਾਉਂਦੀ ਹੈ, ਅਤੇ ਆਪਣਾ ਆਕਾਰ ਕਿੰਨਾ ਚੰਗਾ ਰੱਖਦੀ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਕ੍ਰਿਟੀਕਲ ਡਾਈਮੈਂਸ਼ਨ ਇਕ ਇਕੱਲੇ ਲਿਥੋ ਪਾਸ ਦੀ ਸਮਰੱਥਾ ਤੋਂ ਬਹਿਸ ਹੋ ਜਾਂਦੇ ਹਨ, ਫੈਬ multi-patterning ਵਰਤਦੀਆਂ ਹਨ—ਇੱਕ ਘਣੇ ਪੈਟਰਨ ਨੂੰ ਕਈ ਐਕਸਪੋਜ਼ਰ ਅਤੇ ਟਰਾਂਸਫਰਾਂ ਵਿੱਚ ਭਾਗ ਕਰਨਾ। ਇਸ ਨਾਲ ਸਿਰਫ਼ ਲਿਥੋਗ੍ਰਾਫੀ ਕਦਮ ਨਹੀਂ ਵਧਦੇ; ਇਹ spacer, mandrel, trim, ਅਤੇ cut mask ਲਈ ਸਹਾਇਕ deposition/etch ਲੂਪਾਂ ਨੂੰ ਗੁਣਾ ਕਰ ਦਿੰਦਾ ਹੈ।

ਪੁੰਚਲਾਈਨ: leading-edge ਚਿਪ 'ਤੇ ਪੈਟਰਨ ਇੱਕ ਜਾਂ ਇੱਕੋ ਹੀ ਨਹੀਂ, ਬਲਕਿ ਕਈ deposit ਅਤੇ etch ਚੱਕਰਾਂ ਦਾ ਨਤੀਜਾ ਹੋ ਸਕਦੀ ਹੈ।

ਕਿਉਂਕਿ ਹਰ ਕਦਮ ਅਗਲੇ ਲਈ ਸ਼ੁਰੂਆਤੀ ਹਾਲਤ ਬਦਲ ਦਿੰਦਾ ਹੈ, ਸਭ ਤੋਂ ਵਧੀਆ ਨਤੀਜੇ ਸਮੱਗਰੀ, ਪਲਾਜ਼ਮਾ ਸ਼ਰਤਾਂ, ਚੈਂਬਰ ਸਫ਼ਾਈ, ਅਤੇ ਕਲੀਨਜ਼ ਨੂੰ ਇੱਕ ਲੜੀ ਵੱਜੋਂ ਟਿਊਨ ਕਰਨ ਨਾਲ ਆਉਂਦੇ ਹਨ। ਇੱਕ ਛੋਟੀ ਸੁਧਾਰ ਇਕ etch 'ਚ ਮੁੜ- ਡਿਪੋਜ਼ਿਟ ਦੁਆਰਾ ਮਿਟਾਇਆ ਜਾਂਦਾ (ਜਾਂ ਵਧਾਇਆ) ਜਾ ਸਕਦਾ ਹੈ, ਇਸੀ ਲਈ ਪ੍ਰੋਸੈਸ ਇੰਟਿਗ੍ਰੇਸ਼ਨ ਨੋਹਿਲ ਸਮੇਂ ਨਾਲ ਨਿਰਣಾಯಕ ਬਣਦੀ ਹੈ।

ਪਲੇਨਰ ਟਰਾਂਜ਼ਿਸਟਰ ਜ਼ਿਆਦਾਤਰ "ਚਪੱਟੇ" ਸਨ, ਜਿਸ ਨਾਲ ਬਹੁਤ ਸਾਰੇ ਕਦਮ ਸਤਹ ਨੂੰ ਰੰਗਣ ਅਤੇ ਕੰਚੀ ਦੇ ਵਰਗ ਲੱਗਦੇ ਸਨ। ਸਕੇਲਿੰਗ ਨੇ ਉਦਯੋਗ ਨੂੰ 3D ਵੱਲ ਧੱਕਿਆ: ਪਹਿਲਾਂ FinFETs (ਇੱਕ ਵਰਟਿਕਲ "ਫਿਨ" ਜਿਸਨੂੰ ਗੇਟ ਘੇਰਦਾ ਹੈ), ਅਤੇ ਹੁਣ gate-all-around (GAA) ਜਿੱਥੇ ਗੇਟ ਚੈਨਲ ਨੂੰ ਪੂਰੀ ਤਰ੍ਹਾਂ ਘੇਰਦਾ ਹੈ (ਅਕਸਰ stacked nanosheets ਵਜੋਂ)।

ਜਦ ਫੀਚਰਾਂ ਦੇ ਸਾਈਡਵਾਲ, ਕੋਨੇ, ਅਤੇ ਡੂੰਘੀਆਂ ਖੋਹਾਂ ਹੁੰਦੀਆਂ ਹਨ, deposition ਸਿਰਫ਼ "ਉੱਪਰ" ਨੂੰ ਕੋਟ ਕਰਨ ਵਰਗੀ ਨਹੀਂ ਰਹਿੰਦੀ। ਫਿਲਮਾਂ ਦਾ conformal ਹੋਣਾ ਲਾਜ਼ਮੀ ਹੈ—ਟ੍ਰੈਂਚ ਦੇ ਤਲ 'ਤੇ ਲਗਭਗ ਉਹੀ ਮੋਟਾਈ ਜਿਵੇਂ ਉੱਪਰ ਸਤਹ 'ਤੇ।

ਇਸੇ ਲਈ ALD ਅਤੇ ਧਿਆਨ ਨਾਲ ਟਿਊਨ ਕੀਤੇ CVD ਕਦਮ leading edge 'ਤੇ ਵੱਧ ਮਹੱਤਵਪੂਰਨ ਹੋ ਜਾਂਦੇ ਹਨ: ਸਾਈਡਵਾਲ 'ਤੇ ਕੁਝ ਐਟਮ ਘੱਟ ਹੋਣ ਨਾਲ ਉੱਚ ਰੇਜ਼ਿਸਟੈਂਸ, ਘੱਟ ਭਰੋਸੇਯੋਗਤਾ, ਜਾਂ ਇਕ ਕਮਜ਼ੋਰ ਬੈਰਿਅਰ ਬਣ ਸਕਦੀ ਹੈ ਜੋ ਸਮੱਗਰੀ ਨੂੰ diffuse ਹੋਣ ਦਿੰਦੀ ਹੈ।

Etch ਨੂੰ ਠੀਕ ਪ੍ਰੋਫਾਈਲ ਬਣਾਉਣੀ ਪੈਂਦੀ ਹੈ: ਸਿੱਧੀ ਦੀਵਾਰਾਂ, ਸਾਫ਼ ਤਲ, ਘੱਟ ਰਫ਼ਨੈਸ, ਅਤੇ ਇੱਕ ਸਮੱਗਰੀ ਨੂੰ ਹਟਾਉਂਦੇ ਸਮੇਂ ਦੂਜੀ ਨੂੰ ਬਿਨਾਂ ਚੱਬੇ। ਘਣੇ 3D ਪੈਟਰਨਾਂ ਵਿੱਚ, ਇੱਕ ਛੋਟਾ "ਓਵਰ-etch" ਮਹੱਤਵਪੂਰਨ ਖੇਤਰਾਂ ਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾ ਸਕਦਾ ਹੈ, ਜਦਕਿ "ਅੰਡਰ-etch" ਰੇਜ਼ਿਡਿਊ ਛੱਡ ਸਕਦਾ ਹੈ ਜੋ ਬਾਅਦ ਦੀ ਡਿਪੋਜ਼ਿਟ ਨੂੰ ਰੋਕਦਾ ਹੈ।

ਕਈ ਆਧੁਨਿਕ ਸਰਚਨਾ ਉੱਚ aspect ratio ਹਨ—ਚੌੜਾਈ ਦੇ ਮੁਕਾਬਲੇ ਬਹੁਤ ਡੂੰਘੇ। ਇਨ੍ਹਾਂ 'ਚੋਂ ਬਿਲਕੁਲ ਇੱਕੋ ਜਿਹਾ ਨਤੀਜਾ ਮਿਲਣਾ ਔਖਾ ਹੈ ਕਿਉਂਕਿ ਰੀਏਕਟੈਂਟ, ਆਇਨ, ਅਤੇ ਬਾਇਪ੍ਰੋਡਕਟ ਤੰਗ ਜਗ੍ਹਾਂ 'ਚ ਸਮਾਨ ਤਰੀਕੇ ਨਾਲ ਨਹੀਂ ਚੱਲਦੇ। microloading ਅਤੇ ਸਾਈਡਵਾਲ ਨੁਕਸਾਨ ਜ਼ਿਆਦਾ ਸੰਭਾਵਿਤ ਬਣ ਜਾਂਦੇ ਹਨ।

GAA ਅਤੇ ਅਡਵਾਂਸਡ ਇੰਟਰਕਨੈਕਟ ਨਵੇਂ, ਜਟਿਲ ਮੈਟਰੀਅਲ ਸਟੈਕ ਅਤੇ ਬਹੁਤ ਪਤਲੇ ਇੰਟਰਫੇਸ ਲਿਆਉਂਦੇ ਹਨ। ਇਸ ਨਾਲ ਸਰਫੇਸ ਤਿਆਰੀ ਲਈ ਦਰਜਾ ਵੱਧ ਜਾਂਦਾ ਹੈ: ਪ੍ਰੀ-ਕਲੀਨ, ਨਰਮ ਪਲਾਜ਼ਮਾ ਟ੍ਰੀਟਮੈਂਟ, ਅਤੇ ਅਗਲੇ ਡਿਪੋਜ਼ਿਟ ਤੋਂ ਪਹਿਲਾਂ ਇੰਟਰਫੇਸ ਕੰਟਰੋਲ। ਜਦ "ਸਰਫੇਸ" ਸਿਰਫ਼ ਕੁਝ ਐਟਮ ਪਰਤਾਂ ਹੀ ਹੋਵੇ, ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਇੱਕ ਕੰਮ ਕਰਦਾ ਡਿਵਾਈਸ ਅਤੇ ਇਕ ਜੋ ਬਾਅਦ ਵਿੱਚ ਚੁੱਪਚਾਪ ਫੇਲ ਹੋ ਜਾਂਦਾ ਵਿੱਚ ਅੰਤਰ ਲਿਆਉਂਦਾ ਹੈ।

"Yield" ਸਾਰਲ ਅਰਥ ਵਿੱਚ ਉਹ ਹਿੱਸਾ ਹੈ ਜੋ ਉਮੀਦ ਅਨੁਸਾਰ ਕੰਮ ਕਰਦਾ। ਜੇ ਇੱਕ ਵਾਫਰ ਵਿੱਚ ਹਜ਼ਾਰਾਂ ਡਾਈਜ਼ ਹਨ, ਤਾਂ ਡਿਫੈਕਟ ਦਰ ਵਿੱਚ ਇੱਕ ਛੋਟਾ ਬਦਲਾਅ ਸੈਂਕੜਿਆਂ ਹੋਰ ਵੇਚਣਯੋਗ ਹਿੱਸਿਆਂ ਵਿੱਚ ਤਬਦੀਲ ਹੋ ਸਕਦਾ ਹੈ। ਇਸੀ ਲਈ ਉਦਯੋਗ ਛੋਟੇ-ਛੋਟੇ ਨੰਬਰਾਂ 'ਤੇ ਵੀ ਧਿਆਨ ਦਿੰਦਾ ਹੈ—ਕਿਉਂਕਿ ਸਕੇਲ 'ਤੇ, ਛੋਟੇ ਸੁਧਾਰ ਵਾਸਤਵਿਕ ਉਤਪਾਦਨ ਬਣਾ ਦਿੰਦੇ ਹਨ।

ਕਈ yield ਘਾਟੇ ਮਾਇਕ੍ਰੋ ਸਕੇਲ 'ਤੇ ਵਾਜਬੀ ਦਿੱਸਦੇ ਨਹੀਂ; ਉਹ ਇਲੈਕਟ੍ਰਿਕਲ ਫੇਲਿਯਰਾਂ ਵਜੋਂ ਸਾਹਮਣੇ ਆਉਂਦੇ ਹਨ। ਕੁਝ ਆਮ ਉਦਾਹਰਣ:

Deposition ਅਤੇ etch ਇਹਨਾਂ ਸਾਰੇ ਨੂੰ ਪ੍ਰਭਾਵਿਤ ਕਰ ਸਕਦੇ ਹਨ। ਇੱਕ ਫਿਲਮ ਜੋ ਥੋੜ੍ਹੀ ਘਲਤ ਮੋਟਾਈ, ਸੰਰਚਨਾ, ਜਾਂ ਯੂਨੀਫਾਰਮਿਟੀ ਰੱਖਦੀ ਹੈ, "ਠੀਕ" ਦਿਸ ਸਕਦੀ ਹੈ, ਪਰ ਇਹ ਟਰਾਂਜ਼ਿਸਟਰ ਦੇ ਵਿਹਾਰ ਨੂੰ ਇਸ ਤਰ੍ਹਾਂ ਬਦਲ ਸਕਦੀ ਹੈ ਕਿ ਉਹ ਸਪੀਡ ਜਾਂ ਪਾਵਰ ਟਾਰਗੇਟ ਨੂੰ ਨਹੀਂ ਪੂਰਾ ਕਰਦੀ।

ਭਾਵੇਂ ਕੋਈ ਸੋਚਣ ਯੋਗ ਡਿਫੈਕਟ ਨਾ ਹੋਵੇ, ਵਾਫਰ ਵਿੱਚ (ਜਾਂ ਵਾਫਰ-ਤੋਂ-ਵਾਫਰ) variation aise ਚਿਪ ਬਣਾਉਂਦੀ ਹੈ ਜੋ ਅਸਮਾਨ ਤਰੀਕੇ ਨਾਲ ਕੰਮ ਕਰਦੀਆਂ ਹਨ। ਇੱਕ ਕੋਣਾ ਜ਼ਿਆਦਾ ਗਰਮ ਚੱਲਦਾ ਹੈ, ਹੋਰ ਕੋਣਾ ਸ্লੋ ਹੁੰਦਾ ਹੈ, ਅਤੇ ਅਚਾਨਕ ਪ੍ਰੋਡਕਟ ਬਿਨਿੰਗ ਬਦਲ ਜਾਂਦੀ ਹੈ—ਜਾਂ ਪਰਟ ਫੇਲ ਹੋ ਜਾਂਦਾ ਹੈ। ਡਿਪੋਜ਼ੀਸ਼ਨ ਦਰਾਂ, ਪਲਾਜ਼ਮਾ ਸ਼ਰਤਾਂ, ਅਤੇ etch selectivity 'ਤੇ ਕਸਕੇ ਨਿਯੰਤਰਣ ਇਹ झਟਕਿਆਂ ਨੂੰ ਘਟਾਉਂਦਾ ਹੈ।

ਆਧੁਨਿਕ ਫੈਬ ਪ੍ਰੋਸੈਸ ਨੂੰ ਸਿਰਫ਼ ਅਨੁਭਵ ਨਾਲ ਨਹੀਂ ਟਿਊਨ ਕਰਦੇ। ਉਹ ਮੇਟਰੋਲੋਜੀ (ਮੋਟਾਈ, critical dimensions, ਪ੍ਰੋਫਾਈਲ ਆਕਾਰ, ਯੂਨੀਫਾਰਮਿਟੀ ਮਾਪਣਾ) ਅਤੇ ਇੰਸਪੈਕਸ਼ਨ (ਕਣ, ਪੈਟਰਨ ਡਿਫੈਕਟ, ਐਜ ਮੁੱਦੇ ਲੱਭਣਾ) 'ਤੇ ਨਿਰਭਰ ਕਰਦੇ ਹਨ। ਨਤੀਜੇ ਪ੍ਰੋਸੈਸ ਸਮਾਧਾਨਾਂ 'ਚ ਫੀਡਬੈਕ ਦਿੰਦੇ ਹਨ:

ਅਸਲ ਵਿੱਚ, ਇਹ ਇੱਕ ਸਾਫਟਵੇਅਰ ਸਮੱਸਿਆ ਵੀ ਬਣ ਜਾਂਦੀ ਹੈ: ਟੂਲ, ਮੈਟਰੋਲੋਜੀ, ਅਤੇ ਇੰਸਪੈਕਸ਼ਨ ਤੋਂ ਡੇਟਾ ਨੂੰ ਜੁੜ ਕੇ ਐਸਾ ਕੁਝ ਬਣਾਉਣਾ ਜੋ ਇੰਜੀਨੀਅਰ ਤੇਜ਼ੀ ਨਾਲ ਕਾਰਵਾਈ ਕਰ ਸਕਣ। ਟੀਮ ਅਕਸਰ ਅੰਦਰੂਨੀ ਡੈਸ਼ਬੋਰਡ, ਅਲਰਟਿੰਗ, ਅਤੇ "ਕੀ ਬਦਲਿਆ?" ਟੂਲ ਬਣਾਉਂਦੀਆਂ ਹਨ ਤਾਂ ਕਿ ਸਿਗਨਲ ਤੋਂ ਠੀਕ ਕਰਨ ਤੱਕ ਦਾ ਸਮਾਂ ਘਟੇ। ਪਲੇਟਫਾਰਮਾਂ ਜਿਵੇਂ Koder.ai ਇੱਥੇ ਮਦਦਗਾਰ ਹੋ ਸਕਦੀਆਂ ਹਨ ਕਿ ਪ੍ਰੋਸੈਸ ਅਤੇ ਡੇਟਾ ਟੀਮ ਚੈਟ ਤੋਂ ਹਲਕੀ-ਫਲਕੀ ਵੈੱਬ ਐਪਸ ਸਪੀਡ ਨਾਲ ਬਣਾਉਣ—ਲੰਮੇ ਪੁਰਾਣੇ ਸોફਟਵੇਅਰ ਸਾਈਕਲ ਦੀ ਉਡੀਕ ਕਰਨ ਦੀ ਲੋੜ ਘਟਦੀ ਹੈ।

ਸਭ ਤੋਂ ਕੀਮਤੀ ਨੋਹਿਲ ਇਨਕ੍ਰੀਮੈਂਟਲ ਹੁੰਦੀ ਹੈ: ਹਰ ਨੋਡ ਦੱਸਦਾ ਹੈ ਕਿ ਕਿਸ ਤਰ੍ਹਾਂ ਕੁਝ ਡਿਫੈਕਟ ਸਿਰਜਦੇ ਹਨ, ਕਿਹੜੇ ਸੈੱਟਿੰਗ ਸਮੇਂ ਨਾਲ ਡ੍ਰਿਫਟ ਹੁੰਦੇ ਹਨ, ਅਤੇ ਕਿਹੜੇ ਜੋੜਾਂ ਸਥਿਰ ਰਹਿੰਦੇ ਹਨ। ਉਹ ਸਿੱਖਿਆ ਅੱਗੇ ਚੱਲ ਕੇ ਕੰਮ ਆਉਂਦੀ—ਤਾਂ ਜੋ ਅਗਲਾ ਨੋਡ ਇੱਕ ਚੰਗੀ ਪਲੇਅਬੁੱਕ ਨਾਲ ਸ਼ੁਰੂ ਹੁੰਦਾ ਹੈ, ਖਾਲੀ ਸ਼ੀਟ ਨਾਲ ਨਹੀਂ।

ਇੱਕ deposition ਜਾਂ etch ਟੂਲ ਇਕ ਹੀ "ਸੈਟਿੰਗ" 'ਤੇ ਨਹੀਂ ਚੱਲਦਾ। ਇਹ ਇੱਕ ਰੈਸੀਪੀ 'ਤੇ ਚੱਲਦਾ ਹੈ—ਕਦਮਾਂ ਦੀ ਇੱਕ ਬਣੱਤਰ ਜੋ ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਪ੍ਰੋਸੈਸ ਸਮੇਂ ਦੇ ਨਾਲ ਕਿਵੇ ਹੋਵੇਗਾ। ਰੈਸੀਪੀ ਵਿੱਚ ਕਈ ਫੇਜ਼ ਹੋ ਸਕਦੇ ਹਨ (ਸਥਿਰ ਕਰਨਾ, ਪ੍ਰੀ-ਕਲੀਨ, ਮੁੱਖ ਕਦਮ, ਪੋਸਟ-ਟ੍ਰੀਟਮੈਂਟ), ਹਰ ਇੱਕ ਆਪਣੀਆਂ ਗੈਸ ਫਲੋ, ਦਬਾਅ, ਤਾਪਮਾਨ, RF ਪਾਵਰ, ਸਮਾਂ, ਅਤੇ endpoint ਲਾਜਿਕ ਰੱਖਦਾ ਹੈ। ਇਸ ਵਿੱਚ "ਚੁੱਪ" ਵੇਰਵੇ ਵੀ ਸ਼ਾਮਲ ਹੁੰਦੇ ਹਨ: ਪਰਜ ਸਮੇਂ, ਵਾਫਰ ਹੈਂਡਲਿੰਗ ਵਰਤਾਰਾ, ਅਤੇ ਪਹਿਲੇ ਵਾਫਰ ਤੋਂ ਪਹਿਲਾਂ ਚੈਂਬਰ ਦੀ ਤਿਆਰੀ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਚਿਪ ਨਵੇਂ ਨੋਡਾਂ ਵੱਲ ਜਾਂਦੇ ਹਨ, ਫੈਬ ਨਵੀਆਂ ਸਮੱਗਰੀਆਂ ਅਤੇ 3D ਆਕਾਰ ਲਿਆਉਂਦੇ ਹਨ—ਅਕਸਰ ਇਕੱਠੇ। ਇੱਕ ਫਿਲਮ ਜੋ ਇੱਕ ਫਲੈਟ ਸਤਹ 'ਤੇ ਚੰਗੀ ਕੰਮ ਕਰਦੀ ਸੀ, ਡੂੰਘੇ, ਤੰਗ ਫੀਚਰਾਂ 'ਤੇ ਵੱਖਰੀ ਕੰਮਗਿਰ ਹੋ ਸਕਦੀ ਹੈ। ਇੱਕ etch ਕਦਮ ਜੋ ਪਿਛਲੇ ਜਨਰੇਸ਼ਨ 'ਤੇ ਕਾਫੀ ਸੈਲੇਕਟਿਵ ਸੀ, ਨਵੀਂ liner ਜਾਂ barrier ਨੂੰ ਨੁਕਸਾਨ ਪਹੁੰਚਾਉਣ ਲੱਗ ਸਕਦੀ ਹੈ।

ਇਸ ਲਈ ਰੈਸੀਪੀ ਵਿਕਸਤ ਹੁੰਦੀਆਂ ਰਹਿੰਦੀਆਂ ਹਨ: ਡਿਵਾਈਸ ਲਕਸ਼ (ਸਪੀਡ, ਪਾਵਰ, ਭਰੋਸੇਯੋਗਤਾ) ਬਦਲਦੇ ਹਨ, ਜੀਓਮੀਟਰੀ ਕੱਦੀ ਹੁੰਦੀ ਹੈ, ਅਤੇ ਇੰਟਿਗ੍ਰੇਸ਼ਨ ਰੋਕਟਆਂ ਵਧਦੀਆਂ ਹਨ। ਪ੍ਰੋਸੈਸ ਵਿਕਾਸ ਟਿਊਨਿੰਗ, ਮਾਪਣ, ਅਤੇ ਮੁੜ-ਟਿਊਨਿੰਗ ਦਾ ਲੰਮਾ ਚੱਕਰ ਬਣ ਜਾਂਦਾ ਹੈ—ਕਦੇ-ਕਦੇ ਉਹ ਸਮੱਸਿਆਵਾਂ ਹੱਲ ਕਰਨ ਲਈ ਜੋ ਸਿਰਫ਼ ਹਜ਼ਾਰਾਂ ਵਾਫਰਾਂ ਦੇ ਬਾਅਦ ਹੀ ਸਾਹਮਣੇ ਆਉਂਦੀਆਂ ਹਨ।

ਹਾਈ-ਵਾਲੀਅਮ ਨਿਰਮਾਣ ਵਿੱਚ, ਇੱਕ ਚੈਂਬਰ ਦਾ ਇਕ ਵਾਰ ਵਧੀਆ ਨਤੀਜਾ ਦੇਣਾ ਕਾਫੀ ਨਹੀ—ਦੁਹਰਾਉਣਯੋਗਤਾ ਇਹ ਯਕੀਨ ਦਾਂਦੀ ਹੈ ਕਿ ਇੱਕੋ ਰੈਸੀਪੀ ਵਾਫਰ-ਤੋਂ-ਵਾਫਰ ਇੱਕੋ ਨਤੀਜਾ ਦੇਵੇ। ਟੂਲ-ਟੂਲ ਮੈਚਿੰਗ ਇਹ ਯਕੀਨ ਦਿਲਾਂਦੀ ਹੈ ਕਿ ਇੱਕ ਰੈਸੀਪੀ ਜਦ ਦੂਜੇ ਟੂਲ ਜਾਂ ਦੂਜੇ ਫੈਬ 'ਤੇ ਟ੍ਰਾਂਸਫਰ ਹੋਵੇ ਤਾਂ ਵੀ ਉਹ ਉਨ੍ਹਾਂ ਕਸੇ ਲਿਮਿਟਾਂ ਵਿੱਚ thickness, profile, ਅਤੇ ਯੂਨੀਫਾਰਮਿਟੀ ਨੂੰ ਮਿਲੇ—ਨਹੀਂ ਤਾਂ ਉਤਪਾਦਨ ਯੋਜਨਾ ਅਤੇ yield ਪ੍ਰਭਾਵਿਤ ਹੁੰਦੇ ਹਨ।

ਕੰਟੈਮੀਨੇਸ਼ਨ ਕੰਟਰੋਲ ਵੀ ਇਸ ਹਕੀਕਤ ਦਾ ਹਿੱਸਾ ਹੈ। ਚੈਂਬਰ ਜਿਵੇਂ-ਜਿਵੇਂ ਸਮੇਂ ਨਾਲ films ਨਾਲ ਭਰਦੇ ਜਾਂਦੇ ਹਨ, ਪਲਾਜ਼ਮਾ ਸ਼ਰਤਾਂ ਅਤੇ ਕਣ ਜੋਖਮ ਪ੍ਰਭਾਵਿਤ ਹੁੰਦੇ ਹਨ। ਫੈਬਸ ਚੈਂਬਰ ਕੰਡੀਸ਼ਨਿੰਗ, ਸੀਜ਼ਨਿੰਗ ਰਨ, ਕਲੀਨ, ਅਤੇ ਰੋਜ਼ਾਨਾ ਰੱਖ-ਰਖਾਅ ਸ਼ਡਿਊਲ 'ਤੇ ਨਿਰਭਰ ਕਰਦੇ ਹਨ ਤਾਂ ਕਿ ਪ੍ਰੋਸੈਸ ਸਮੇਂ ਨਾਲ ਸਥਿਰ ਰਹੇ। ਇਹ ਕਾਰਜਕਾਰੀ ਨੋਹਿਲ—ਕਿਵੇਂ ਰੈਸੀਪੀ ਮਹੀਨਿਆਂ ਨਹੀਂ, ਮਿੰਟਾਂ ਲਈ ਕੰਮ ਕਰਦੀ ਰਹੇ—ਹੀ ਅਨੁਭਵ ਦੇ ਨਾਲ ਗੁਣਾ ਹੁੰਦੀ ਹੈ।

Leading-edge ਚਿਪਸ ਸਿਰਫ਼ ਟੂਲ ਖਰੀਦ ਕੇ, ਇਸ ਨੂੰ ਇੰਸਟਾਲ ਕਰਕੇ, ਅਤੇ "ਰੱਨ" ਦਬਾਕੇ ਨਹੀਂ ਬਣਾਈਆਂ ਜਾਂਦੀਆਂ। Deposition ਅਤੇ etch ਕਦਮ ਚਿਪ ਦੇ ਲੇਆਉਟ, ਸਮੱਗਰੀ ਸਟੈਕ, ਅਤੇ ਭਰੋਸੇਯੋਗਤਾ ਲਕਸ਼ਾਂ ਨਾਲ ਗੰਢੇ ਹੋਏ ਹਨ, ਇਸ ਲਈ ਉਪਕਰਨ ਬਣਾਉਣ ਵਾਲੇ ਅਤੇ ਫੈਬ ਚਲਾਉਣ ਵਾਲੇ ਲੋਕ ਇਕੱਠੇ ਇਟਰੇਟ ਕਰਦੇ ਹਨ।

ਚਿਪ ਡਿਜ਼ਾਇਨਰ ਉਹ ਢਾਂਚੇ ਨਿਰਧਾਰਤ ਕਰਦੇ ਹਨ ਜੋ ਉਹਨਾਂ ਨੂੰ ਚਾਹੀਦੇ ਹਨ (ਉਦਾਹਰਣ ਲਈ, ਛੋਟੇ contacts, ਉੱਚ vias, ਨਵੇਂ ਮੈਟਲ ਸਟੈਕ)। ਪ੍ਰੋਸੈਸ ਇੰਟੀਗ੍ਰੇਸ਼ਨ ਟੀਮਾਂ ਫੈਬ ਦੇ ਅੰਦਰ ਇਸ ਡਿਜ਼ਾਈਨ ਨੂੰ ਇੱਕ ਕਦਮ-ਬਾਈ-कਦਮ ਫਲੋ ਵਿੱਚ ਤਬਦੀਲ ਕਰਦੀਆਂ ਹਨ: ਇਸ ਲੇਅਰ ਨੂੰ ਡਿਪੋਜ਼ਿਟ ਕਰੋ, ਪੈਟਰਨ ਕਰੋ, etch ਕਰੋ, ਕਲੀਨ ਕਰੋ, ਅਤੇ ਦੁਹਰਾਓ। Lam Research ਵਰਗੇ ਟੂਲ ਨਿਰਮਾਤਾ ਫਿਰ ਉਹਨਾਂ ਲੋੜਾਂ ਨੂੰ ਅਸਲ ਹਾਰਡਵੇਅਰ 'ਤੇ ਮੈਨੂਫੈਕਚਰਬਲ ਰੈਸੀਪੀਜ਼ ਵਿੱਚ ਤਬਦੀਲ ਕਰਨ ਵਿੱਚ ਮਦਦ ਕਰਦੇ ਹਨ।

ਉਹ ਹੱਥ-ਇੱਕਬਾਰੀ ਹੌਂਦ-ਦੌਰ ਵਿੱਚ ਇੱਕ ਲੂਪ ਬਣ ਜਾਂਦਾ ਹੈ: ਸ਼ੁਰੂਆਤੀ ਦੌੜਾਂ ਸਮੱਸਿਆਵਾਂ (ਪ੍ਰੋਫਾਈਲ ਡ੍ਰਿਫਟ, ਰੇਜ਼ਿਡਿਊ, ਲਾਈਨ-ਐਜ ਰਫ਼ਨੈਸ, ਅਣਉਮੀਦDamage) ਨੂੰ ਦਰਸਾਉਂਦੀਆਂ ਹਨ, ਅਤੇ ਫੀਡਬੈਕ ਪ੍ਰੋਸੈਸ ਫਲੋ ਅਤੇ ਟੂਲ ਸੈਟਿੰਗਜ਼ ਦੋਹਾਂ ਨੂੰ ਵਾਪਸ ਜਾਂਦਾ—ਕਦੇ-ਕਦੇ ਹਾਰਡਵੇਅਰ ਵਿਕਲਪਾਂ ਤੱਕ ਜਿਵੇਂ ਚੈਂਬਰ ਮੈਟਰੀਅਲ, ਪਲਾਜ਼ਮਾ ਸੋਰਸ, ਜਾਂ ਗੈਸ ਡਿਲਿਵਰੀ।

Leading edge 'ਤੇ, ਤੁਸੀਂ deposition ਜਾਂ etch ਨੂੰ ਅਲੱਗ ਤੋਂ ਠੀਕ ਨਹੀਂ ਕਰ ਸਕਦੇ ਕਿਉਂਕਿ ਹਰ ਕਦਮ ਅਗਲੇ ਲਈ ਸ਼ੁਰੂਆਤ ਨੂੰ ਬਦਲਦਾ ਹੈ। ਇੱਕ ਛੋਟਾ ਬਦਲਾਅ ਫਿਲਮ ਡੈਂਸਿਟੀ 'ਚ etch ਦਰ ਨੂੰ ਬਦਲ ਸਕਦਾ ਹੈ; ਇੱਕ ਜ਼ਿਆਦਾ ਐਗਰੈਸੀਵ etch ਬਾਅਦ ਦੀ deposition ਨੂੰ ਘੱਟ conformal ਬਣਾ ਸਕਦਾ ਹੈ। Co-optimization ਸੰਗਤ ਕਰਦੀ ਹੈ:

ਫੈਬਸ ਹਮੇਸ਼ਾਂ throughput vs. precision ਨੂੰ ਤੋਲਦੇ ਹਨ: ਤੇਜ਼ ਪ੍ਰੋਸੈਸਿੰਗ ਵੈਰੀਏਬਿਲਟੀ ਵਧਾ ਸਕਦੀ ਹੈ, ਜਦਕਿ ਬਹੁਤ ਕਸਕ ਕੰਟਰੋਲ ਨਾਲ wafers per hour ਘਟ ਸਕਦੇ ਹਨ। ਓਸੇ ਤਰ੍ਹਾਂ, selectivity vs. damage ਇੱਕ ਮੁੜ-ਮੁੜ ਆਉਣ ਵਾਲੀ ਟਕਰਾਅ ਹੈ: ਇੱਕ ਅਜਿਹਾ etch ਜੋ ਇਕ ਸਮੱਗਰੀ ਨੂੰ ਮਜ਼ਬੂਤੀ ਨਾਲ ਪਸੰਦ ਕਰਦਾ ਹੈ, ਹੋ ਸਕਦਾ ਹੈ ਕਿ ਹਾਰਸ਼ਰ ਹਾਲਤਾਂ ਮੰਗੇ ਜੋ ਰਫ਼ਨੈਸ ਜਾਂ ਡਿਫੈਕਟਿਵਿਟੀ ਦਾ ਖਤਰਾਂ ਪੈਦਾ ਕਰਦੇ ਹਨ।

ਮੁੱਲ-ਭਾਗ ਵਿੱਚ ਦਿੱਤੀ ਜਾਣ ਵਾਲੀ ਮੁੱਖ ਕਦਰ ਜਾਰੀ ਇੰਟিগ੍ਰੇਸ਼ਨ ਸਹਾਇਤਾ ਹੈ—ਸਾਈਟ-ਤੇ ਟਰਬਲਸ਼ੂਟਿੰਗ, ਚੈਂਬਰਾਂ 'ਤੇ ਪ੍ਰਦਰਸ਼ਨ ਮੈਚ ਕਰਨਾ, excursions ਘਟਾਉਣਾ, ਅਤੇ yield ਹਿਲਣ 'ਤੇ ਤੇਜ਼ੀ ਨਾਲ ਬਹਾਲ ਕਰਨ ਵਿੱਚ ਮਦਦ ਕਰਨਾ। ਹਾਈ-ਵਾਲੀਅਮ ਨਿਰਮਾਣ ਲਈ, ਇਹ ਭਾਈਚਾਰਾ ਟੂਲ ਦੇ spec sheet ਦੇ ਉਦਯੋਗਿਕ ਮੁੱਲ ਜਿਤਨਾ ਹੀ ਮਹੱਤਵਪੂਰਨ ਹੋ ਸਕਦਾ ਹੈ।

ਇੱਕ deposition ਜਾਂ etch ਟੂਲ spec sheet 'ਤੇ ਸ਼ਾਨਦਾਰ ਦਿਸ ਸਕਦਾ ਹੈ—ਜਦ ਤੱਕ ਇਹ 24/7 ਚੱਲ ਕੇ ਹਜ਼ਾਰਾਂ ਵਾਫਰਾਂ 'ਤੇ ਉਹੀ ਨਤੀਜੇ ਨਹੀਂ ਦਿੰਦਾ। ਹਾਈ-ਵਾਲੀਅਮ ਨਿਰਮਾਣ ਵਿੱਚ, ਭਰੋਸੇਯੋਗਤਾ ਅਤੇ ਅਪਟਾਈਮ "ਚੰਗੀ ਹੋਣੀ" ਨਾ ਹੀ ਇਕ ਵਿਕਲਪ ਹੈ। ਉਹ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਨਿਰਧਾਰਿਤ ਕਰਦੇ ਹਨ ਕਿ ਇੱਕ ਫੈਬ ਕਿੰਨੇ ਚੰਗੇ ਵਾਫਰ ਜਮਾ ਕਰ ਸਕਦੀ ਹੈ।

Deposition ਅਤੇ etch ਪ੍ਰੋਸੈਸ ਸਥਿਰਤਾ 'ਤੇ ਜੀਉਂਦੇ ਅਤੇ ਮਰਦੇ ਹਨ। ਗੈਸ ਫਲੋ, ਚੈਂਬਰ ਦਬਾਅ, ਪਲਾਜ਼ਮਾ ਪਾਵਰ, ਜਾਂ ਤਾਪਮਾਨ ਵਿੱਚ ਥੋੜ੍ਹੀ ਡ੍ਰਿਫਟ ਵੀ ਫਿਲਮ ਮੋਟਾਈ, ਸਾਈਡਵਾਲ ਐਂਗਲ, ਜਾਂ ਨੁਕਸਾਨ ਪੱਧਰ ਨੂੰ ਬਦਲ ਸਕਦੀ ਹੈ—ਇੱਕ ਕੰਮ ਕਰ ਰਹੀ ਰੈਸੀਪੀ ਨੂੰ yield ਘਟਾਉਣ ਵਾਲੀ ਬਣਾਕੇ।

ਇਸ ਲਈ ਅੱਗੇ-ਪੰਛਲੇ ਟੂਲ (ਜਿਨ੍ਹਾਂ ਵਿੱਚ Lam Research ਸਿਸਟਮ ਵੀ ਸ਼ਾਮਲ ਹਨ) ਰਪੀਟੇਬਲ ਹਾਰਡਵੇਅਰ 'ਚ ਭਾਰੀ ਨਿਵੇਸ਼ ਕਰਦੇ ਹਨ: ਸਥਿਰ RF ਡਿਲਿਵਰੀ, ਕਿਸ਼ਤੀ ਮਾਸ ਫਲੋ ਕੰਟਰੋਲ, ਠੀਕ ਥਰਮਲ ਮੈਨੇਜਮੈਂਟ, ਅਤੇ ਸੈਂਸਰ ਜੋ excursions ਨੂੰ ਜਲਦੀ ਫੜ ਸਕਣ।

ਭਾਵੇਂ ਪ੍ਰੋਸੈਸ ਪਰਫੈਕਟ ਹੋਵੇ, ਉਤਪਾਦਨ ਉਸ ਵੇਲੇ ਪ੍ਰਭਾਵਿਤ ਹੁੰਦੀ ਹੈ ਜਦ ਟੂਲ ਬਾਰ-ਬਾਰ ਡਾਊਨ ਹੁੰਦੇ ਹਨ। ਅਸਲੀ ਫੈਬ ਆਉਟਪੁੱਟ ਇਹਨਾਂ ਨਾਲ ਰੂਪ ਲੈਂਦਾ ਹੈ:

ਇੱਕ ਟੂਲ ਜੋ ਸੇਵਾ ਕਰਨ ਵਿੱਚ ਆਸਾਨ ਹੈ—ਅਤੇ ਮਜ਼ਬੂਤ ਸਪੇਅਰਸ ਫੋਰਕਾਸਟਿੰਗ ਨਾਲ ਸਮਰਥਿਤ ਹੈ—ਉਸ ਨਾਲ ਹੋਰ ਚੈਂਬਰ ਚੱਲਦੇ ਰਹਿਣਗੇ ਅਤੇ ਹੋਰ ਲੌਟ ਹਿਲਦੇ ਰਹਿਣਗੇ।

ਉੱਚ ਅਪਟਾਈਮ ਆਮ ਤੌਰ 'ਤੇ ਪਰ ਵਾਫਰ ਲਾਗਤ ਘਟਾਉਂਦਾ ਹੈ: ਘੱਟ ਖਾਲੀ ਸਮੇਂ ਵਾਲੇ ਆਪਰੇਟਰ, ਮਹਿੰਗੇ ਕਲੀਨਰੂਮ ਸਪੇਸ ਦੀ ਬਿਹਤਰੀ ਵਰਤੋਂ, ਅਤੇ ਮੁੜ ਕੰਮ 'ਤੇ ਲੱਗਣ ਵਾਲਾ ਸਮਾਂ ਘੱਟ। ਇੱਕ ਹੋਰ ਹਕੀਕਤ: ਲੈਬ ਡੈਮੋ ਤੋਂ ਮਾਸ ਉਤਪਾਦਨ ਤੱਕ ਪਹੁੰਚਣਾ ਟੂਲਾਂ ਨੂੰ ਵੱਖਰੇ ਤਰੀਕੇ ਨਾਲ ਤਾਣਦਾ ਹੈ। ਵਧੇ ਹੋਏ ਰਨ, ਜ਼ਿਆਦਾ ਵਾਫਰ ਸਟਾਰਟ, ਅਤੇ ਕੜੇ ਡਿਫੈਕਟ ਬਜਟ ਕਮਜ਼ੋਰੀਆਂ ਨੂੰ ਤੇਜ਼ੀ ਨਾਲ ਬਾਹਰ ਲਿਆਉਂਦੇ ਹਨ—ਇਸ ਲਈ ਭਰੋਸੇਯੋਗਤਾ ਇੰਜੀਨੀਅਰਿੰਗ "ਪ੍ਰੋਸੈਸ ਸਮਰੱਥਾ" ਦਾ ਮੁੱਖ ਹਿੱਸਾ ਬਣ ਜਾਂਦੀ ਹੈ।

ਜਿਵੇਂ-ਜਿਵੇਂ ਚਿਪ ਛੋਟੇ ਨੋਡਾਂ ਅਤੇ ਹੋਰ 3D ਸਟਰਕਚਰਾਂ ਵੱਲ ਵਧ ਰਹੇ ਹਨ, ਪ੍ਰਗਤੀ ਅਕਸਰ deposition ਅਤੇ etch ਕਦਮਾਂ ਨੂੰ extremes ਨਾਲ ਦੁਹਰਾਉਣ 'ਤੇ ਨਿਰਭਰ ਹੋ ਰਹੀ ਹੈ—ਅਕਸਰ ਇੱਕ ਡਿਵਾਈਸ ਸਟੈਕ ਵਿੱਚ ਸੈਂਕੜਿਆਂ ਵਾਰੀ। "ਅਗਲ੍ਹਾ ਬੋਟਲਨੈਕ" ਆਮ ਤੌਰ 'ਤੇ ਕਿਸੇ ਇੱਕ ਹੀ ਬ੍ਰੇਕਥਰੂ 'ਤੇ ਨਹੀਂ, ਬਲਕਿ ਹਰ ਚੱਕਰ ਨੂੰ ਸਥਿਰ ਰੱਖਣ ਦੀ ਕਮਪਰਕਠਿਨਾਈ 'ਤੇ ਹੈ, ਜ਼ੀਵਾਦਾਰ yield, ਵੈਰੀਏਬਿਲਟੀ ਨੂੰ ਕੰਟਰੋਲ ਕਰਨ ਅਤੇ ਨਵੀਆਂ ਪ੍ਰਕਿਰਿਆਵਾਂ ਨੂੰ ਤੇਜ਼ੀ ਨਾਲ ਰੈਂਪ ਕਰਨ 'ਤੇ।

ਕਈ ਰੁਝਾਨ ਹਨ ਜੋ deposition/etch 'ਤੇ ਸਭ ਤੋਂ ਜ਼ਿਆਦਾ ਦਬਾਅ ਪਾਉਣਗੇ:

ਜਦ ਤੁਸੀਂ ਟੂਲ ਵੇਂਡਰ ਜਾਂ ਫੈਬ ਦ੍ਰਿਸ਼ਟੀਕੋਣ (ਜਿਵੇਂ Lam Research ਅਤੇ ਸਮਕੱਖ) ਦੀ ਤੁਲਨਾ ਕਰੋ, ਨਤੀਜਿਆਂ 'ਤੇ ਧਿਆਨ ਦਿਓ:

ਅੱਗੇ ਜਾਣ ਲਈ, /blog 'ਤੇ ਸੰਬੰਧਤ ਵਿਆਖਿਆਵਾਂ ਵੇਖੋ। ਜੇ ਤੁਸੀਂ ਵਿਕਲਪਾਂ ਦਾ ਮੁਲਾਂਕਣ ਕਰ ਰਹੇ ਹੋ—ਜਾਂ yield, excursions, ਅਤੇ ramp ਮੈਟ੍ਰਿਕਸ ਦਾ ਵਿਸ਼ਲੇਸ਼ਣ ਕਰਨ ਲਈ ਅੰਦਰੂਨੀ ਟੂਲ ਬਣਾ ਰਹੇ ਹੋ—/pricing ਵੇਖੋ ਕਿ ਅਸੀਂ ਖਰਚ, ਗਤੀ, ਅਤੇ ਸਮਰੱਥਾ ਬਾਰੇ ਕਿਵੇਂ ਸੋਚਦੇ ਹਾਂ (ਜਦੋਂ ਇੱਕ build-with-chat ਪਲੇਟਫਾਰਮ ਜਿਵੇਂ Koder.ai ਜ਼ਿਆਦਾ ਹੌਲੀ ਲੇਗਸੀ ਸਾਫਟਵੇਅਰ ਪਾਈਪਲਾਈਨ ਦੀ ਥਾਂ ਲੈ ਸਕਦਾ ਹੈ)।

Deposition ਉਹ "ਜੋੜਨ" ਕਦਮ ਹੈ: ਟੂਲ ਵਾਫਰ 'ਤੇ ਬਹੁਤ ਪਤਲੀ ਪਰਤਾਂ ਰੱਖਦੇ ਹਨ (ਲੋਹੇ, ਡਾਇਇਲੈਕਟ੍ਰਿਕ, ਬੈਰਿਅਰ, ਲਾਈਨਰ, ਹਾਰਡਮਾਸਕ)। Etch ਉਹ "ਹਟਾਉਣ" ਕਦਮ ਹੈ: ਟੂਲ ਖਾਸ ਸਮੱਗਰੀ ਨੂੰ ਚੁਣੀਂਦਾ ਤੌਰ 'ਤੇ ਕੱਦਦੇ ਹਨ ਤਾਂ ਕਿ ਪੈਟਰਨ ਟਰਾਂਸਫਰ ਹੋਣ ਅਤੇ ਵਿਸ਼ੇਸ਼ ਫੀਚਰ ਬਣ ਸਕਣ।

ਸਕੇਲਿੰਗ nanometer ਪੈਮਾਨਿਆਂ 'ਤੇ ਥICKਨੈਸ, ਆਕਾਰ ਅਤੇ ਇੰਟਰਫੇਸ ਨੂੰ ਕੰਟਰੋਲ ਕਰਨ 'ਤੇ ਨਿਰਭਰ ਕਰਦੀ ਹੈ, ਇਸ ਲਈ deposition/etch ਦੀ ਗੁਣਵੱਤਾ ਸਿੱਧੇ ਤੌਰ 'ਤੇ ਪ੍ਰਦਰਸ਼ਨ ਅਤੇ yield 'ਤੇ ਪ੍ਰਭਾਵ ਪਾਂਦੀ ਹੈ।

“Leading-edge” ਆਮ ਤੌਰ 'ਤੇ ਉਹ ਸਭ ਤੋਂ ਅੱਡਵਾਂਸਡ ਨੋਡਾਂ ਨੂੰ ਕਹਿੰਦਾ ਹੈ ਜਿੱਥੇ ਹਾਈ-ਵਾਲੀਉਮ ਉਤਪਾਦਨ ਹੁੰਦਾ ਹੈ—ਜਿੱਥੇ ਡੈਵਾਈਸ ਸਟ੍ਰਕਚਰ ਅਤੇ ਸਮੱਗਰੀ ਨਵੀਆਂ ਹੁੰਦੀਆਂ ਹਨ ਅਤੇ ਸੁਤੰਤਰਤਾ ਘੱਟ ਹੁੰਦੀ ਹੈ।

ਇਹ ਕਿਸੇ ਮਾਰਕੀਟਿੰਗ ਨੰਬਰ ਬਾਰੇ ਨਹੀਂ, ਸਗੋਂ ਉਸ ਹਾਲਤ ਬਾਰੇ ਹੈ ਜਿੱਥੇ ਪ੍ਰੋਸੈਸ ਵਿਂਡੋਜ਼ ਘੱਟ ਅਤੇ ਛੋਟੀ ਵੈਰੀਏਸ਼ਨਾਂ ਲਈ ਸੰਵੇਦਨਸ਼ੀਲਤਾ ਜ਼ਿਆਦਾ ਹੁੰਦੀ ਹੈ।

ਕਿਉਂਕਿ ਆਧੁਨਿਕ ਚਿਪ ਇੱਕ ਹੀ ਚੱਕਰ ਵਿੱਚ ਬਣ ਰਹੇ ਹਨ:

ਜਿਵੇਂ-ਜਿਵੇਂ ਫੀਚਰ ਛੋਟੇ ਅਤੇ ਸਟੈਕ ਜਿਆਦਾ ਜਟਿਲ ਹੁੰਦੇ ਹਨ, ਇੱਕ “ਲੇਅਰ” ਅਕਸਰ ਮਨਚਾਹੇ ਮਾਪ ਤੇ ਪਹੁੰਚਣ ਲਈ ਕਈ deposit–etch–clean ਚੱਕਰ ਮੰਗਦੀ ਹੈ।

Conformality ਇਸ ਗੱਲ ਨੂੰ ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਇੱਕ ਫਿਲਮ 3D ਫੀਚਰਾਂ ਦੇ ਟੌਪ, ਸਾਈਡਵਾਲ ਅਤੇ ਤਲ ਨੂੰ ਕਿੰਨਾ ਸਮਾਨ ਤਰੀਕੇ ਨਾਲ ਕੋਟ ਕਰਦੀ ਹੈ।

ਇਹ ਮਹੱਤਵਪੂਰਨ ਹੈ ਕਿਉਂਕਿ ਗੈਰ-ਰੋਪਿਤ ਕਵਰਨੀ:

ਜਦੋਂ conformality ਜ਼ਰੂਰੀ ਹੁੰਦੀ ਹੈ ਤਾਂ ALD ਵਰਗੀਆਂ ਤਕਨੀਕਾਂ ਅਕਸਰ ਵਰਤੀ ਜਾਂਦੀਆਂ ਹਨ।

Selectivity ਇਸ ਗੱਲ ਨੂੰ ਦਰਸਾਉਂਦੀ ਹੈ ਕਿ ਇਕ etch ਇੱਕ ਸਮੱਗਰੀ ਨੂੰ ਦੂਜੀ ਨਾਲੋਂ ਕਿੰਨੀ ਤੇਜ਼ੀ ਨਾਲ ਹਟਾਉਂਦਾ ਹੈ (ਅਕਸਰ ਇੱਕ “etch stop” ਪਰਤ)।

ਚੰਗੀ selectivity ਤੁਹਾਨੂੰ ਸਹਾਇਤਾ ਕਰਦੀ ਹੈ:

ਫੋਟੋਰੇਜ਼ਿਸਟ ਅਕਸਰ ਗਹਿਰੇ/ਨਾਜ਼ੁਕ etch ਸਹਿਣ ਲਈ ਬਹੁਤ ਪਤਲਾ ਜਾਂ ਨਾਜ਼ੁਕ ਹੁੰਦਾ ਹੈ। ਇੱਕ ਹਾਰਡਮਾਸਕ ਸਟੈਕ resist ਪੈਟਰਨ ਅਤੇ ਹੇਠਾਂ ਵਾਲੀ ਫਿਲਮ ਦਰਮਿਆਨ ਇੱਕ ਮਜ਼ਬੂਤ “ਟਰਾਂਸਲੇਟਰ” ਵਜੋਂ ਕੰਮ ਕਰਦਾ ਹੈ।

ਆਮ ਫਲੋ:

ਹਾਰਡਮਾਸਕ ਚੋਣਾਂ etch ਰੋਧ, selectivity, ਅਤੇ ਪ੍ਰੋਫਾਈਲ ਕੰਟਰੋਲ ਦੁਆਰਾ ਨਿਰਧਾਰਤ ਹੁੰਦੀਆਂ ਹਨ।

Multi-patterning ਇੱਕ ਘਣੇ ਪੈਟਰਨ ਨੂੰ ਕਈ ਪੈਟਰਨ-ਟ੍ਰਾਂਸਫਰ ਕਦਮਾਂ ਵਿੱਚ ਵੰਡ ਦਿੰਦਾ ਹੈ ਜਦੋਂ ਇੱਕ ਹੀ lithography ਪਾਸ ਆਖਰੀ pitch ਨੂੰ ਭਰੋਸੇਯੋਗ ਤਰੀਕੇ ਨਾਲ ਨਹੀਂ ਨਿਰਧਾਰਿਤ ਕਰ ਸਕਦੀ।

ਇਸ ਨਾਲ spacer ਜਾਂ mandrel ਬਣਾਉਣ ਵਰਗੇ ਸਪੋਰਟਿੰਗ ਕਦਮ ਜੋੜੇ ਜਾਂਦੇ ਹਨ, ਜਿਸ ਨਾਲ ਇੱਕ ਅੰਤਿਮ ਫੀਚਰ ਸੈੱਟ ਬਣਾਉਣ ਲਈ ਹੋਰ deposit + etch آپਰੇਸ਼ਨ (ਅਤੇ ਕਲੀਨ ਅਤੇ ਮੈਟ੍ਰੋਲੋਜੀ) ਦੀ ਲੋੜ ਵੱਧ ਜਾਂਦੀ ਹੈ।

High aspect ratio ਫੀਚਰਾਂ (ਚੌੜਾਈ ਦੇ ਮੁਕਾਬਲੇ ਬਹੁਤ ਗਹਿਰੇ) transport ਨੂੰ ਮੁਸ਼ਕਲ ਬਣਾਉਂਦੇ ਹਨ:

ਨਤੀਜਾ: ਪ੍ਰੋਫਾਈਲ ਸਮੱਸਿਆਵਾਂ (notching/footing), ਰੇਜ਼ਿਡਿਊ, ਰਫ਼ਨੈਸ, ਅਤੇ ਵੈਰੀਏਬਿਲਟੀ ਦਾ ਜੋਖਮ ਵੱਧ ਜਾਂਦਾ ਹੈ—ਇਸ ਲਈ ਪ੍ਰੋਸੈਸ ਟਿਊਨਿੰਗ ਕਾਫੀ ਸਖ਼ਤ ਹੋਣੀ ਪੈਂਦੀ ਹੈ।

Yield ਉਹ ਹਿੱਸਾ ਹੈ ਜੋ ਰੂਪ ਵਿੱਚ ਕੰਮ ਕਰਦਾ ਹੈ। Deposition ਅਤੇ etch yield 'ਤੇ ਪ੍ਰਭਾਵ ਪਾਉਂਦੇ ਹਨ ਕਿਉਂਕਿ ਉਹ ਡਿਫੈਕਟ ਅਤੇ ਵੈਰੀਏਬਿਲਟੀ ਪੈਦਾ ਕਰਦੇ ਹਨ ਜੋ ਇਲੈਕਟ੍ਰਿਕਲ ਫੇਲਿਯਰ ਬਣ ਜਾਂਦੇ ਹਨ, ਜਿਵੇਂ:

ਅੱਗੇਲੇ ਨੋਡਾਂ 'ਤੇ ਵੀ ਛੋਟੇ ਡ੍ਰਿਫਟ ਡਿਵਾਈਸ ਨੂੰ ਸਪੈਸ ਤੋਂ ਬਾਹਰ ਧਕੇ ਦੇ ਸਕਦੇ ਹਨ।

ਟੂਲ ਦੇ ਸਪੈਸ-ਸ਼ੀਟ ਤੋਂ ਇਲਾਵਾ, ਉਤਪਾਦਨ ਵਿੱਚ ਅਸਲੀ ਫਰਕ ਅਕਸਰ ਪ੍ਰੋਸੈਸ ਨੋਹਿਲ ਹੁੰਦਾ ਹੈ: ਰੈਸੀਪੀ, ਇੰਟਿਗ੍ਰੇਸ਼ਨ ਸੀਕੈਂਸ, ਡਿਫੈਕਟ ਲਰਨਿੰਗ, ਅਤੇ ਟੂਲ-ਟੂ-ਟੂਲ ਮੈਚਿੰਗ।

ਇਹ ਨੋਹਿਲ ਕਿਉਂ ਬਣਦੀ ਹੈ:

ਇਹ ਤਜਰਬਾ ਇੱਕ ਜਨਰੇਸ਼ਨ ਤੋਂ ਦੂਜੇ ਜਨਰੇਸ਼ਨ ਵਿੱਚ ਜੁੜਦਾ ਗਿਆ ਅਤੇ ਨਵੇਂ ਨੋਡਾਂ ਨੂੰ ਮੁੜ-ਸਿੱਖਣ ਦੀ ਲੋੜ ਘਟਾਉਂਦਾ ਹੈ। ਇਹੀ ਕਾਰਨ ਹੈ ਕਿ ਉਪਕਰਨ ਕੰਪਨੀਆਂ ਜਿਵੇਂ ਅੱਗੇ-ਪੰਛਲਾ ਨਿਰਮਾਣ ਵਿੱਚ ਰਣਨੀਤਕ ਮਹੱਤਵ ਰੱਖਦੀਆਂ ਹਨ।