Tại sao lắng đọng và etch đứng ở trung tâm của việc thu nhỏ chip

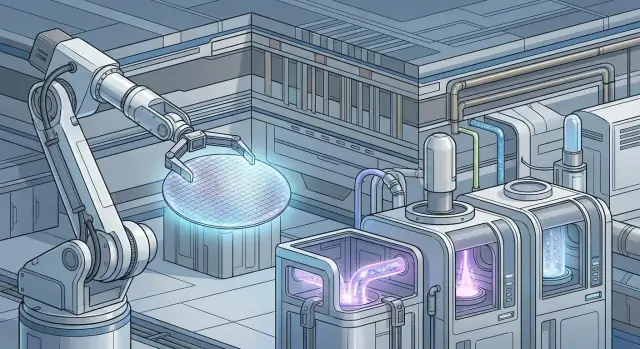

Nếu bóp gọn sản xuất chip xuống những động tác lặp lại nhất, hai bước xuất hiện liên tục: lắng đọng và khắc (etch).

Lắng đọng là bước “thêm”. Các công cụ phủ lên wafer những lớp siêu mỏng—dẫn điện, cách điện, hoặc lớp ngăn—đôi khi chỉ vài nguyên tử một lần. Etch là bước “loại bỏ”. Công cụ khắc chọn lọc để tạo ra các cấu trúc tí hon thành transistor và đường dẫn, lý tưởng là không làm hỏng các lớp bên dưới.

Khi chip thu nhỏ, hai bước này trở thành các nút điều chỉnh chính mà kỹ sư dùng để kiểm soát những gì quan trọng ở kích thước nanomet: độ dày, hình dạng và giao diện. Đó là lý do các công ty thiết bị như Lam Research đứng gần trung tâm của sản xuất tiên tiến.

“Leading-edge” thực sự nghĩa là gì

“Leading-edge” thường chỉ các node tiên tiến nhất, sản xuất với khối lượng lớn—nơi mật độ, tiêu chí công suất và hiệu năng khắt khe nhất, và biên độ lỗi nhỏ nhất. Nó không chỉ là một con số marketing; đó là nơi các cấu trúc thiết bị và vật liệu mới xuất hiện đầu tiên.

Lợi thế tích lũy

Năng lực công cụ thì quan trọng (độ đồng đều, tính chọn lọc, kiểm soát tổn thương, thông lượng). Nhưng kiến thức quy trình cũng quan trọng không kém: các công thức, mẹo tích hợp, phản hồi đo lường và bài học về khiếm khuyết biến một công cụ tốt thành quy trình sản xuất ổn định, tỷ lệ sản phẩm đạt chuẩn cao.

Lợi thế này tích lũy theo thế hệ công nghệ vì mỗi node mới không bắt đầu từ con số 0—nó xây trên kinh nghiệm trước đó về cách các màng phát triển, plasma hành xử ra sao, và các biến thể nhỏ ảnh hưởng lớn tới tỷ lệ thành phẩm.

Những gì ta sẽ bàn tiếp

Để thấy tại sao chu kỳ lắng đọng và etch cứ nhân lên, ta sẽ xem xét:

- Patterning ở giới hạn và lý do tại sao các vòng “deposit–etch–clean” lặp lại lại phổ biến

- Cấu trúc 3D (các đặc trưng tỉ lệ cao) khó lấp đầy và khó khắc hơn

- Học về tỷ lệ sản phẩm, khiếm khuyết và biến động—nơi kinh nghiệm trả tiền

- Vòng phản hồi giữa nhà sản xuất công cụ và fab giúp tăng tốc cải thiện

Từ các lớp đến logic: Chip hiện đại thực sự được xây như thế nào

Chip hiện đại không bị “gia công” từ một khối silicon. Nó được lắp ghép—giống như một chiếc bánh nhiều lớp ở kích thước vi mô—bằng cách liên tục thêm các lớp siêu mỏng, định hình chúng và loại bỏ có chọn lọc những gì không cần. Làm điều đó hàng trăm lần, bạn có các transistor, đường dẫn và lớp cách điện xếp chồng và quấn lẫn nhau trong 3D.

Vòng lặp lặp: thêm, định hình, loại bỏ

Ở mức cao, sản xuất chip đi theo nhịp điệu quen thuộc:

- Lắng đọng phủ một lớp (kim loại, oxide, nitride, v.v.), thường chỉ vài nguyên tử đến vài nanomet.

- Patterning xác định chỗ lớp đó được giữ lại (dùng lithography để tạo mặt nạ).

- Etch loại bỏ vùng phơi bày, chuyển mẫu vào lớp.

Mỗi vòng tạo ra một “lát” của thiết bị cuối cùng—cấu trúc cổng, lỗ tiếp xúc, hoặc đường dẫn—cho đến khi logic và bộ nhớ của chip xuất hiện từ ngăn xếp.

Tại sao các đặc trưng nhỏ yêu cầu kiểm soát cực kỳ chặt

Khi các đặc trưng đo bằng nanomet một chữ số, kiểm soát độ dày và hình dạng không còn là “điều tốt nên có”. Một lớp hơi dày có thể chặn một khe hẹp; một etch hơi mạnh có thể làm rộng đường hoặc làm xước lớp bên dưới. Ngay cả thay đổi nhỏ về profile—góc thành, bo góc, độ nhám—cũng có thể làm thay đổi cách điện chạy.

Bước quy trình, cửa sổ quy trình và tỷ lệ sản phẩm

Sản xuất được tổ chức thành các bước quy trình (các thao tác lắng đọng/etch cụ thể) phải chạy trong một cửa sổ quy trình—phạm vi thiết lập mà kết quả ổn định. Khi chip trở nên dày đặc hơn, các cửa sổ này thu hẹp. Và vì các lớp sau xây trên các lớp trước, một sai lệch nhỏ có thể kéo theo lệch trục, chập mạch, đứt mạch và cuối cùng giảm tỷ lệ sản phẩm đạt chuẩn.

Lắng đọng 101: Phủ lớp với độ kiểm soát ở cấp nguyên tử

Lắng đọng là nửa “thêm vật liệu” của sản xuất chip: xây các lớp siêu mỏng trên wafer để các bước sau có thể định hình, bảo vệ hoặc cách điện những gì bên dưới. Những lớp này không phải để trang trí—mỗi lớp được chọn cho một nhiệm vụ cụ thể và phải hoạt động tin cậy trên hàng tỷ cấu trúc nhỏ.

Ba phương pháp chính: CVD, PVD, và ALD

Chemical Vapor Deposition (CVD) dùng các khí phản ứng tạo màng rắn trên bề mặt wafer. Nó được dùng rộng rãi cho nhiều lớp điện môi và một số lớp dẫn vì phủ đều trên diện tích lớn và cho độ đồng đều tốt.

Physical Vapor Deposition (PVD) (thường gọi là “sputtering”) bắn các nguyên tử khỏi mục tiêu và lắng đọng lên wafer. PVD phổ biến cho kim loại và vật liệu hardmask, đặc biệt khi cần màng dày, nhưng nó gặp khó khăn khi phủ thành bên của các cấu trúc rất sâu, hẹp.

Atomic Layer Deposition (ALD) phủ vật liệu từng “liều” phân tử qua các phản ứng bề mặt tự hạn chế. Nó chậm hơn nhưng xuất sắc khi cần kiểm soát và bao phủ—đặc biệt ở các cấu trúc 3D chật hẹp nhất.

Khi chip chuyển sang fin, trench và lỗ đứng, lắng đọng không còn là vấn đề “sơn lớp trên” đơn giản. Conformality mô tả mức độ mà một lớp phủ đều mặt trên, thành bên và đáy của một cấu trúc.

Nếu một lớp mỏng ở thành bên hoặc bị đóng miệng ở đầu mở, bạn có thể gặp rò điện, lấp không đầy hoặc lỗi ở các bước etch sau. Độ phủ đồng đều cao là bắt buộc cho các cấu trúc sâu, hẹp nơi dung sai rất nhỏ.

Tính chất màng có thể quyết định tỷ lệ sản phẩm

Ngay cả khi độ dày đúng, màng phải đáp ứng một số yêu cầu thực tế:

- Độ đồng đều: độ dày nhất quán trên toàn wafer và giữa các wafer.

- Tạp chất: nguyên tử không mong muốn có thể thay đổi hành vi điện hoặc gây vấn đề độ tin cậy.

- Ứng suất: màng quá kéo (tensile) hay nén (compressive) có thể làm cong hoặc nứt cấu trúc.

- Bám dính: các lớp phải dính chắc qua chu kỳ nhiệt, làm sạch và etch.

Ví dụ trực quan: các lớp làm gì

- Liner phủ thành bên để bảo vệ bề mặt và tạo điều kiện bắt đầu cho việc lấp đầy sau đó.

- Barrier ngăn kim loại khuếch tán vào vật liệu xung quanh (quan trọng cho độ tin cậy).

- Hardmasks như các stencil bền chịu được etch mạnh hơn so với photoresist.

- Lớp điện môi cách điện và tách rời các dẫn—thiết yếu để tránh chập mạch.

Ở leading edge, lắng đọng không chỉ là “thêm một lớp.” Đó là kỹ thuật vật liệu chính xác, tinh chỉnh để mỗi bước etch và pattern tiếp theo hoạt động dự đoán được.

Etch 101: Khắc cấu trúc mà không làm hỏng thứ bên dưới

Etch là nửa “loại bỏ” của sản xuất chip: sau khi lớp được phủ và mẫu resist tạo, etch loại bỏ vật liệu phơi bày để chuyển mẫu vào lớp bên dưới. Bí quyết là hiếm khi bạn muốn loại bỏ mọi thứ—bạn muốn loại bỏ một vật liệu cụ thể nhanh chóng trong khi dừng trên vật liệu khác. Tính chất đó gọi là selectivity, và nó là lý do tại sao các fab tiên tiến đầu tư nhiều vào kiến thức quy trình etch (và tại sao nhà cung cấp thiết bị như Lam Research dành nhiều năm để tinh chỉnh).

Tại sao selectivity quan trọng

Một ngăn xếp hiện đại có thể gồm silicon, silicon oxide, silicon nitride, kim loại và hard mask. Trong quá trình etch, bạn có thể cần làm sạch một lớp mà vẫn giữ lớp “etch stop” nguyên vẹn. Selectivity kém có thể làm mỏng các lớp quan trọng, thay đổi kích thước transistor hoặc tạo đường rò làm giảm tỷ lệ sản phẩm.

Etch plasma, về mặt khái niệm

Hầu hết etch tiên tiến dùng plasma: một khí áp suất thấp được kích năng thành các loài phản ứng.

Hai điều xảy ra cùng lúc:

- Hoá học: các gốc phản ứng tạo sản phẩm bay hơi với vật liệu mục tiêu (để được bơm ra).

- Hướng tính: trường điện làm tăng tốc ion về phía wafer, tạo thành thành phần “thẳng đứng” giúp khắc rãnh và lỗ tiếp xúc hẹp.

Cân bằng hai yếu tố này là nghệ thuật: quá nhiều hoá học sẽ ăn ngầm, quá nhiều năng lượng ion sẽ gây tổn thương.

Etch “tốt” trông như thế nào

Các đội quy trình thường theo đuổi vài kết quả sau:

- Thành bên thẳng đứng (để đặc trưng trùng với hình dạng mong muốn)

- Tổn thương tối thiểu (ít làm nhám bề mặt, ít điện tích bị giữ, ít phá vỡ tinh thể)

- Profile lặp lại wafer-to-wafer và tool-to-tool (để các bước hạ nguồn hoạt động dự đoán)

Thách thức phổ biến khi etch

Ngay cả khi công thức “đúng,” wafer thực tế vẫn gây khó:

- Microloading: vùng dày đặc và thưa thớt etch với tốc độ khác nhau.

- Footing/notching: méo profile gần giao diện hoặc lớp etch-stop.

- Độ nhám: kết cấu thành bên làm tăng điện trở hoặc biến động.

- Dư lượng: polymer hoặc vật liệu tái lắng đọng gây cản trở deposition hoặc làm sạch sau đó.

Ở các node dẫn đầu, quản lý những chi tiết này thường là sự khác biệt giữa demo trong phòng thí nghiệm và sản xuất quy mô lớn.

Patterning ở giới hạn: Tại sao chu kỳ Etch/Lắng đọng nhân lên

Biến dữ liệu fab thành ứng dụng

Tạo dashboard đơn giản cho tỷ lệ sản phẩm đạt chuẩn và theo dõi sự cố từ chat, rồi triển khai khi cần.

Khi người ta tưởng tượng việc thu nhỏ chip, họ thường nghĩ đến một máy “đột phá” in các đường nhỏ hơn. Thực tế, việc chuyển mẫu bị giới hạn bởi chuỗi—resist, hardmask, selectivity etch, ứng suất lớp và làm sạch—chứ không phải một công cụ kỳ diệu.

Hardmask stack: mẫu cần một “bộ dịch”

Photoresist tốt để bắt mẫu, nhưng thường mỏng và dễ hỏng khi phải chịu các etch sâu, chính xác cần trong thiết bị hiện đại. Vì vậy các fab xây hardmask stack—những lớp được lựa chọn cẩn thận phủ trên lớp đích.

Lưu đồ đơn giản là:

- Deposit một hoặc nhiều lớp hardmask (thường là vật liệu khác nhau để tăng selectivity).

- Etch mẫu resist vào hardmask.

- Etch mẫu hardmask vào lớp đích.

- Strip/clean, rồi lặp lại khi cần.

Mỗi lớp phủ được chọn không chỉ vì bản thân nó, mà vì cách nó hành xử trong etch kế tiếp: tốc độ etch so với lớp kề, độ nhám tạo ra, và khả năng giữ hình dạng.

Multi-patterning: một đặc trưng thành nhiều bước

Khi kích thước quan trọng nhỏ hơn khả năng của một lần phơi sáng, các fab dùng multi-patterning—chia một mẫu dày đặc thành nhiều phơi sáng và chuyển mẫu. Điều đó không chỉ thêm bước lithography; nó nhân lên các vòng lặp deposition/etch cho spacer, mandrel, trim và mặt nạ cắt.

Điểm then chốt: “mẫu” trên một chip leading-edge có thể là kết quả của vài chu kỳ deposit và etch với kiểm soát chặt chẽ.

Tại sao tuning đầu-cuối quan trọng

Vì mỗi bước thay đổi điều kiện bắt đầu cho bước kế tiếp, kết quả tốt nhất đến từ việc tinh chỉnh toàn bộ chuỗi—vật liệu, điều kiện plasma, độ sạch buồng và công đoạn làm sạch—như một hệ thống duy nhất. Một cải thiện nhỏ trong một etch có thể bị xoá (hoặc khuếch đại) bởi deposition kế tiếp, nên kiến thức tích hợp quy trình trở thành lợi thế theo thời gian.

Transistor 3D và tỉ lệ cao làm tăng độ khó

Transistor phẳng từng là “mặt phẳng,” khiến nhiều bước giống như quét và cắt bề mặt. Việc thu nhỏ đẩy ngành vào 3D: đầu tiên là FinFET (một “fin” đứng được gate quấn quanh), và giờ là gate-all-around (GAA) nơi gate bao quanh hoàn toàn kênh (thường là các nanosheet xếp chồng).

Tại sao 3D thay đổi lắng đọng

Khi cấu trúc có thành bên, góc và khoang sâu, lắng đọng không còn là “phủ trên cùng.” Màng phải conformal—gần như cùng độ dày ở đáy trench như ở bề mặt trên.

Đó là lý do các kỹ thuật như ALD và các bước CVD tinh chỉnh quan trọng hơn ở leading edge: thiếu vài nguyên tử ở thành bên có thể làm tăng điện trở, giảm độ tin cậy, hoặc làm yếu lớp ngăn.

Tại sao 3D làm etch khó tính hơn

Etch phải tạo profile đúng: thành thẳng, đáy sạch, độ nhám tối thiểu và loại bỏ chọn lọc một vật liệu mà không ăn vào lớp bên dưới. Trong các mẫu 3D dày đặc, ngay cả “over-etch” nhỏ cũng có thể làm xước vùng quan trọng, còn “under-etch” để lại dư lượng chắn việc lắng đọng sau đó.

Tỉ lệ cao: cạm bẫy đồng đều

Nhiều cấu trúc hiện đại có tỉ lệ cao—rất sâu so với hẹp. Đạt kết quả đồng đều trên hàng tỷ cấu trúc như vậy khó vì phản ứng, ion và sản phẩm phụ không di chuyển đồng đều vào/ra các khe hẹp. Vấn đề như microloading và tổn thương thành bên trở nên phổ biến.

Vật liệu mới đem lại bề mặt mới

GAA và liên kết nội bộ nâng cao mang theo ngăn xếp vật liệu phức tạp hơn và giao diện mỏng. Điều đó nâng tiêu chuẩn cho chuẩn bị bề mặt: tiền làm sạch, xử lý plasma nhẹ và kiểm soát giao diện trước bước lắng đọng tiếp theo. Khi “bề mặt” chỉ mỏng vài lớp nguyên tử, kiến thức quy trình quyết định giữa thiết bị hoạt động và thiết bị thất bại dần dần.

Tỷ lệ sản phẩm, khiếm khuyết và biến động: nơi kiến thức quy trình trả tiền

“Yield” đơn giản là phần chip trên wafer hoạt động như mong muốn. Nếu một wafer có hàng nghìn chip, một thay đổi nhỏ trong tỷ lệ khiếm khuyết có thể là hàng trăm phần hơn sản phẩm bán được. Đó là lý do các nhà sản xuất chú ý tới các con số nhỏ—vì ở quy mô lớn, cải thiện nhỏ trở thành sản lượng thực.

Khiếm khuyết trở thành vấn đề điện thế nào

Nhiều tổn thất yield không nhìn thấy rõ dưới kính hiển vi; chúng xuất hiện dưới dạng lỗi điện. Một vài ví dụ phổ biến:

- Opens: một đường dẫn bị mỏng hoặc đứt, nên dòng không thể chảy.

- Shorts: hai cấu trúc lẽ ra phải tách biệt lại chạm nhau, tạo kết nối không mong muốn.

- Leakage: lớp điện môi quá mỏng, xốp hoặc bị hỏng, cho phép dòng rò.

Các bước lắng đọng và etch có thể ảnh hưởng tất cả các vấn đề này. Một màng hơi sai về độ dày, thành phần hoặc đồng đều có thể trông “ổn” nhưng đủ để làm thay đổi hành vi transistor, khiến nó không đạt mục tiêu tốc độ hoặc tiêu thụ điện.

Biến động: kẻ giết yield thầm lặng

Ngay cả khi không có khiếm khuyết rõ rệt, biến động trên wafer (hoặc giữa các wafer) tạo nên các chip hoạt động không đồng đều. Một góc nóng hơn, một góc chạy chậm hơn, và đột nhiên phân loại sản phẩm thay đổi—hoặc linh kiện hỏng. Kiểm soát chặt tốc độ lắng đọng, điều kiện plasma và selectivity etch giảm những dao động này.

Metrology và inspection như vô lăng điều khiển

Các fab hiện đại không điều chỉnh quy trình bằng trực giác. Họ dựa vào metrology (đo độ dày, kích thước quan trọng, hình dạng profile, đồng đều) và inspection (tìm hạt, khiếm khuyết mẫu, vấn đề mép). Kết quả phản hồi vào các điều chỉnh quy trình:

- Nếu profile trôi, điều chỉnh hoá học etch hoặc thời gian.

- Nếu màng thay đổi độ dày, sửa thông số deposition.

- Nếu dấu hiệu khiếm khuyết tăng, kỹ sư truy nguồn tới module cụ thể, điều kiện buồng hoặc lô vật liệu.

Trên thực tế, điều này cũng tạo ra bài toán phần mềm: khâu dữ liệu từ công cụ, metrology và inspection lại để kỹ sư hành động nhanh. Các đội thường xây dashboard nội bộ, cảnh báo và công cụ “có gì thay đổi?” để rút ngắn khoảng thời gian từ tín hiệu đến sửa lỗi. Các nền tảng như Koder.ai có thể giúp bằng cách cho phép đội quy trình và dữ liệu dựng nhanh các web app nhẹ từ chat—hữu ích để tích hợp KPI yield, ghi chú sự cố và lịch sử chạy mà không phải chờ vòng phát triển dài.

Học hỏi tích lũy qua các node

Kiến thức giá trị nhất là từng bước: mỗi node dạy điều gì gây ra khiếm khuyết nhất định, thiết lập nào trôi theo thời gian, và tổ hợp nào ổn định. Những bài học đó mang sang node tiếp theo—vì vậy node sau bắt đầu bằng một playbook tốt hơn, không phải tờ trắng.

Công thức, tính lặp lại và trò dài hơi của phát triển quy trình

Lập kế hoạch trước khi xây dựng

Lên bản đồ công cụ nội bộ tiếp theo trước khi viết code bằng Koder.ai Planning Mode.

Một công cụ lắng đọng hay etch không chạy bằng một “thiết lập” đơn. Nó chạy theo công thức—một chuỗi có cấu trúc các bước định nghĩa cách quy trình diễn ra theo thời gian. Một công thức có thể gồm nhiều pha (ổn định, tiền làm sạch, bước chính, xử lý sau), mỗi pha có lưu lượng khí, áp suất, nhiệt độ, công suất RF, thời gian và logic điểm kết thúc riêng. Nó cũng bao gồm các chi tiết “âm thầm”: thời gian purge, hành vi di chuyển wafer và cách buồng được chuẩn bị trước wafer đầu.

Tại sao công thức thay đổi liên tục

Khi chip chuyển sang node mới, fab đưa vào vật liệu mới và hình dạng 3D mới—thường cùng lúc. Một màng từng hoạt động trên bề mặt phẳng có thể hành xử khác trong các cấu trúc sâu, hẹp. Một bước etch từng đủ chọn lọc thế hệ trước có thể bắt đầu làm hỏng một liner hoặc barrier mới.

Đó là lý do công thức tiến hoá: mục tiêu thiết bị thay đổi (tốc độ, công suất, độ tin cậy), hình học thắt lại, và ràng buộc tích hợp tăng. Phát triển quy trình trở thành chu trình dài của điều chỉnh, đo lường và điều chỉnh lại—đôi khi để giải quyết các vấn đề chỉ xuất hiện sau hàng nghìn wafer.

Lặp lại, khớp và giữ sạch

Trong sản xuất quy mô lớn, một buồng không chỉ cần tạo kết quả tốt một lần. Tính lặp lại nghĩa là cùng một công thức cho cùng một kết quả từ wafer này sang wafer khác. Khớp tool-to-tool nghĩa là khi chuyển công thức sang công cụ khác (hoặc fab khác) vẫn đạt độ dày, profile và đồng đều trong giới hạn chặt—nếu không lập kế hoạch và yield sẽ bị ảnh hưởng.

Kiểm soát ô nhiễm là một phần của thực tế này. Buồng “lão hóa” khi các lớp tích tụ trên bề mặt trong buồng, ảnh hưởng điều kiện plasma và rủi ro hạt. Các fab dựa vào điều kiện buồng, chạy ủ, làm sạch và lịch bảo trì phòng ngừa để quy trình ổn định theo thời gian. Kiến thức vận hành—làm sao để công thức giữ hiệu năng trong tháng chứ không phải phút—là nơi kinh nghiệm cộng dồn.

Tại sao nhà sản xuất công cụ và fab tối ưu cùng nhau, không hoạt động riêng rẽ

Chip tiên tiến không được sản xuất bằng cách mua một công cụ, lắp nó và bấm “chạy”. Các bước lắng đọng và etch gắn chặt với bố cục chip, ngăn xếp vật liệu và mục tiêu độ tin cậy, nên những người làm thiết bị và người vận hành fab thường tương tác lặp lại.

Bàn giao là một vòng lặp, không phải một đường thẳng

Nhà thiết kế chip định nghĩa cấu trúc cần (ví dụ contact nhỏ hơn, via cao hơn, ngăn xếp kim loại mới). Các đội tích hợp quy trình trong fab chuyển thiết kế đó thành một luồng: phủ lớp này, pattern, etch, clean, lặp lại. Các nhà cung cấp công cụ như Lam Research giúp biến yêu cầu đó thành công thức sản xuất trên phần cứng thực.

Bàn giao nhanh chóng trở thành vòng lặp: các lần chạy đầu phơi bày vấn đề (drift profile, dư lượng, thô mép, tổn thương không mong muốn), và phản hồi đi trở lại cả luồng quy trình và cài đặt công cụ—đôi khi còn dẫn đến thay đổi phần cứng như vật liệu buồng, nguồn plasma hoặc hệ cấp khí.

Tối ưu cùng nhau giữa vật liệu, phần cứng và luồng

Ở leading edge, bạn không thể tối ưu lắng đọng hoặc etch một mình vì mỗi bước thay đổi điều kiện bắt đầu cho bước kế tiếp. Một thay đổi nhỏ về mật độ màng có thể thay đổi tốc độ etch; etch quyết liệt hơn có thể làm deposition sau đó kém conformal. Tối ưu cùng nhau căn chỉnh:

- Lựa chọn vật liệu (điện môi mới, hard mask, barrier)

- Năng lực công cụ (hoá học plasma, kiểm soát nhiệt độ, xử lý wafer)

- Trình tự quy trình (chuỗi etch/deposition nhiều bước, làm sạch, điểm đo lường)

Những đánh đổi có thật—và được quản lý cẩn thận

Các fab liên tục cân bằng thông lượng vs. độ chính xác: xử lý nhanh hơn có thể tăng biến động, trong khi kiểm soát cực chặt có thể giảm wafer/giờ. Tương tự, selectivity vs. tổn thương là căng thẳng lặp lại: etch chọn lọc mạnh có thể cần điều kiện khắc nghiệt làm tăng độ nhám hoặc khiếm khuyết.

Hỗ trợ tích hợp là một phần của sản phẩm

Một phần quan trọng của giá trị là hỗ trợ tích hợp liên tục—khắc phục tại chỗ, khớp hiệu suất giữa các buồng, giảm sự cố và giúp phục hồi nhanh khi yield thay đổi. Đối với sản xuất quy mô lớn, mối quan hệ này có thể quan trọng ngang tầm thông số kỹ thuật của công cụ.

Từ năng lực công cụ đến sản lượng fab: độ tin cậy và thời gian hoạt động quan trọng

Tạo mẫu công cụ quy trình nhanh chóng

Tạo mẫu giao diện báo cáo đo lường bằng React với backend Go và Postgres qua chat.

Một công cụ lắng đọng hoặc etch có thể nhìn tuyệt trên spec—cho đến khi nó phải chạy 24/7, trên hàng nghìn wafer, với cùng kết quả mỗi lần. Trong sản xuất quy mô lớn, độ tin cậy và thời gian hoạt động không phải “điều tốt nên có”. Chúng quyết định trực tiếp bao nhiêu wafer tốt fab có thể giao.

Kiểm soát chặt là mục tiêu chính

Lắng đọng và etch sống chết bởi độ ổn định quy trình. Dịch nhỏ trong lưu lượng khí, áp suất buồng, công suất plasma, hay nhiệt độ có thể làm thay đổi độ dày màng, góc thành hoặc mức tổn thương—biến công thức hoạt động thành mất yield.

Đó là lý do các công cụ hàng đầu (bao gồm hệ thống của Lam Research) đầu tư mạnh vào phần cứng lặp lại: RF ổn định, kiểm soát lưu lượng chính xác, quản lý nhiệt và cảm biến bắt sớm sự cố.

Sản lượng phụ thuộc bảo trì ngang vật lý

Ngay cả khi quy trình hoàn hảo, sản xuất vẫn bị ảnh hưởng khi công cụ thường xuyên dừng. Sản lượng thực tế bị định hình bởi:

- Bảo trì theo kế hoạch (làm sạch, ủ buồng, thay kit)

- Thời gian chết ngoài kế hoạch (sự kiện hạt, mất ổn định plasma, sự cố bơm)

- Logistics phụ tùng (có sẵn vật tư tiêu hao trên site)

Một công cụ dễ bảo trì—và được hỗ trợ bằng dự báo phụ tùng tốt—giữ nhiều buồng hoạt động hơn và giữ các lô di chuyển.

Độ tin cậy trở thành chi phí và lịch trình

Thời gian hoạt động cao thường hạ chi phí trên wafer: ít thời gian nhân công đứng không, tận dụng tốt không gian sạch đắt tiền và ít thời gian cho sửa lại. Còn quan trọng hơn, tính sẵn sàng nhất quán làm cho lịch giao hàng trở nên dự đoán được, điều quan trọng khi các bước sau được xếp chồng sát nhau.

Một thực tế nữa: chuyển từ demo phòng thí nghiệm sang sản xuất khối lượng lớn đặt áp lực khác lên công cụ. Chạy dài, tăng wafer start và ngân sách khiếm khuyết chặt lọc nhanh các điểm yếu—do đó kỹ thuật độ tin cậy trở thành phần cốt lõi của “năng lực quy trình”.

Những gì cần theo dõi tiếp theo: áp lực thu nhỏ và nút thắt tiếp theo của quy trình

Khi chip tiến vào node nhỏ hơn và cấu trúc 3D nhiều hơn, tiến bộ ngày càng dựa vào lặp lại các bước lắng đọng và etch với độ chính xác cực cao—thường hàng trăm lần trong một ngăn xếp thiết bị. “Nút thắt tiếp theo” thường không phải một đột phá duy nhất, mà là khó khăn tích lũy khi giữ mọi chu kỳ đồng đều trong khi duy trì yield, kiểm soát biến động và ramp quy trình nhanh đủ để đáp ứng nhu cầu.

Nơi áp lực hội tụ

Một số xu hướng có thể làm tăng áp lực lên lắng đọng/etch:

- Kiến trúc thiết bị mới (GAA/nanosheet, CFET): không gian chặt và lớp mỏng tăng độ nhạy với sai số độ dày hoặc độ sâu etch.

- Cung cấp điện mặt sau (backside power delivery): thêm bề mặt mới, bước tích hợp mới và chế độ lỗi mới phải quản lý mà không làm hỏng phía trước.

- Quy trình chọn lọc: phụ thuộc nhiều hơn vào “đặt ở đây, không đặt ở kia” và “etch vật này, không phải vật kia”, nâng tiêu chuẩn cho selectivity và kiểm soát khiếm khuyết.

- Độ phức tạp vật liệu: nhiều màng kỳ lạ hơn, liner và barrier phải đồng đều, ít lỗi và tương thích xuống dòng.

- Tốc độ ramp mong đợi: chuyển node không chỉ đánh giá bằng năng lực mà còn bằng tốc độ ổn định yield ở khối lượng.

Danh sách kiểm tra nhanh cho người không chuyên

Khi so sánh nhà cung cấp công cụ hoặc cách tiếp cận fab (bao gồm Lam Research và đối thủ), hãy tập trung vào kết quả:

- Cải thiện yield: Quy trình giảm khiếm khuyết chết người ở quy mô không?

- Kiểm soát biến động: Kết quả trong wafer và giữa wafer chặt tới mức nào?

- Tốc độ ramp: Bao nhanh một node mới đạt sản xuất ổn định, quy mô lớn?

- Tính lặp lại và thời gian hoạt động: Công cụ giữ ổn định trong các chu trình dài với ít thời gian chết chứ?

Để đi sâu hơn, browse related explainers on /blog. Nếu bạn đang đánh giá lựa chọn—hoặc xây công cụ nội bộ để phân tích yield, sự cố và số liệu ramp—see /pricing để hiểu cách chúng tôi nghĩ về chi phí, tốc độ và năng lực (bao gồm khi nền tảng build-with-chat như Koder.ai có thể thay thế một đường ống phần mềm legacy chậm).