04. Mai 2025·8 Min

Lam Research und der kumulative Vorteil in der Chipfertigung

Wie Abscheide‑ und Ätzwerkzeuge führende Chips formen, warum Prozess‑Know‑how sich über die Zeit aufschichtet und was das für Ausbeuten, Nodes und Skalierung bedeutet.

Wie Abscheide‑ und Ätzwerkzeuge führende Chips formen, warum Prozess‑Know‑how sich über die Zeit aufschichtet und was das für Ausbeuten, Nodes und Skalierung bedeutet.

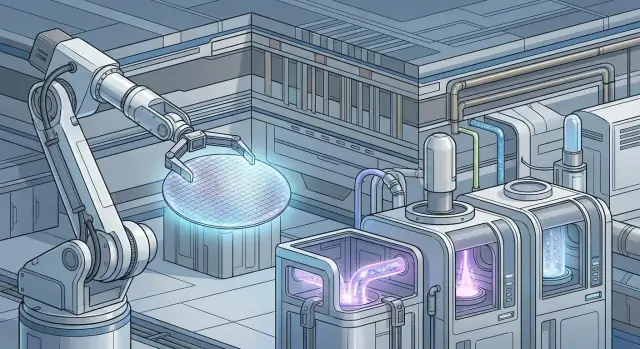

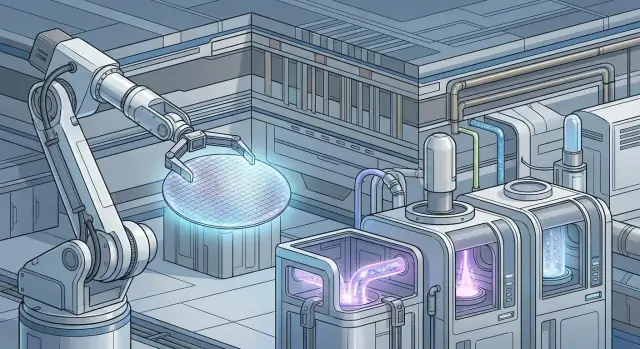

Wenn Sie die Chipherstellung auf ihre wiederholbaren Grundbewegungen reduzieren, erscheinen zwei Aktionen immer wieder: Deposition und Etch.

Deposition ist der „Hinzufügen“-Schritt. Werkzeuge legen ultradünne Filme ab — Leiter, Isolatoren oder spezielle Barrierschichten — manchmal nur wenige Atome auf einmal. Etch ist der „Entfernen“-Schritt. Werkzeuge fräsen selektiv Material weg, um die winzigen Strukturen zu schaffen, die später Transistoren und Verdrahtung bilden, idealerweise ohne die darunter liegenden Schichten zu schädigen.

Mit der Skalierung wurden diese beiden Schritte zu den primären Stellschrauben, mit denen Ingenieure auf Nanometerebene das Wichtigste kontrollieren: Dicke, Form und Grenzflächen. Deshalb sitzen Ausrüster wie Lam Research nahe am Kern der führenden Fertigung.

„Leading‑Edge“ bezieht sich im Allgemeinen auf die fortschrittlichsten, volumenstarken Produktions‑Nodes — dort, wo Dichte, Leistung und Energieziele am aggressivsten sind und der Fehlerbereich am kleinsten. Es geht nicht nur um eine Marketingzahl; hier tauchen neue Gerätearchitekturen und Materialien zuerst auf.

Die Fähigkeiten eines Werkzeugs sind wichtig (Uniformität, Selektivität, Schadenskontrolle, Durchsatz). Aber Prozess‑Know‑how ist mindestens genauso entscheidend: die Rezepte, Integrationstricks, metrologischen Rückkopplungen und das Lernen aus Defekten, die aus einem guten Werkzeug einen stabilen, ausbeute‑starken Fabrikprozess machen.

Dieser Vorteil akkumuliert über Technologie‑Generationen, weil jeder neue Node nicht bei Null beginnt — er baut auf früheren Erkenntnissen darüber auf, wie Schichten wachsen, wie Plasmen sich verhalten und wie kleine Variationen große Ausbeuteschwankungen auslösen.

Um zu verstehen, warum sich Deposition–Etch‑Zyklen vervielfachen, betrachten wir:

Ein moderner Chip wird nicht aus einem Block Silizium „gefräst“. Er wird zusammengesetzt — eher wie eine mikroskopische Schichttorte — indem ultradünne Filme wiederholt aufgebracht, gemustert und selektiv entfernt werden. Macht man das hunderte Male, entstehen Transistoren, Leitungen und Isolationsbarrieren gestapelt und verschränkt in 3D.

Auf hoher Ebene folgt die Chipherstellung einem vertrauten Rhythmus:

Jede Schleife erzeugt eine „Scheibe“ des Endgeräts — Gate‑Strukturen, Kontaktlöcher oder Interconnect‑Leitungen — bis die Logik und der Speicher des Chips aus dem Stapel hervorgehen.

Wenn Features in einstelligen Nanometern gemessen werden, ist Kontrolle über Dicke und Form keine „Nice‑to‑have“-Anforderung mehr. Ein Film, der etwas zu dick ist, kann eine enge Öffnung verengen; ein zu aggressives Ätzen kann eine Linie verbreitern oder eine darunter liegende Schicht anritzen. Schon kleine Profiländerungen — Seitenwandwinkel, Eckabrundung, Oberflächenrauheit — können den Stromfluss verschieben.

Die Fertigung ist in Prozessschritte organisiert (spezifische Deposition/Etch‑Operationen), die innerhalb eines Prozessfensters laufen müssen — dem Bereich von Parametern, in dem die Ergebnisse konsistent akzeptabel sind. Mit zunehmender Dichte schrumpfen diese Fenster. Und weil spätere Schichten auf früheren aufbauen, kann eine kleine Abweichung in eine Fehlausrichtung, Kurzschlüsse, Unterbrechungen und letztlich niedrigere Ausbeute eskalieren.

Deposition ist die „Material hinzufügen“-Hälfte der Chipherstellung: ultradünne Filme auf einem Wafer aufbauen, damit spätere Schritte das darunterliegende schützen, mustern oder elektrisch isolieren können. Diese Filme sind nicht dekorativ — jede Schicht ist für eine spezifische Aufgabe gewählt und muss über Milliarden winziger Features hinweg zuverlässig funktionieren.

Chemical Vapor Deposition (CVD) nutzt reaktive Gase, die eine feste Schicht auf der Waferoberfläche bilden. Es wird häufig für viele dielektrische und einige leitfähige Schichten verwendet, weil es große Flächen effizient und mit guter Uniformität bedeckt.

Physical Vapor Deposition (PVD) (oft „Sputtern“) schlägt Atome von einem Target los und deponiert sie auf dem Wafer. PVD ist bei Metallen und Hardmask‑Materialien üblich, besonders wenn man einen dichten Film will — es kann jedoch Schwierigkeiten haben, Seitenwände sehr tiefer, schmaler Strukturen zu beschichten.

Atomic Layer Deposition (ALD) trägt Material dosisweise durch selbstlimitierende Oberflächenreaktionen auf. Es ist langsamer, liefert aber exzellente Kontrolle und Abdeckung, was in den engsten 3D‑Features wichtiger ist als Geschwindigkeit.

Mit der Entwicklung zu Fins, Gräben und vertikalen Löchern wurde Deposition kein reines „oben anstreichen“-Problem mehr. Konformität beschreibt, wie gleichmäßig ein Film oberhalb, an den Seitenwänden und am Boden eines Features aufgetragen wird.

Wenn eine Schicht an der Seitenwand dünn ist oder an der Öffnung zustopft, kann es zu elektrischen Lecks, schlechtem Fill oder Ausfällen in späteren Ätzschritten kommen. Hohe Konformität ist für tiefe, schmale Features mit sehr geringer Fehlertoleranz entscheidend.

Auch wenn die Dicke korrekt ist, muss der Film mehrere praktische Anforderungen erfüllen:

An der Spitze der Fertigung ist Deposition nicht nur „einen Film auftragen“. Es ist präzises Materialengineering, so abgestimmt, dass jeder nachfolgende Ätz‑ und Pattern‑Schritt vorhersehbar reagiert.

Etch ist die „subtraktive“ Hälfte der Chipherstellung: nachdem ein Film deponiert und mit Resist gemustert wurde, entfernt Etch exponiertes Material, um das Muster in die darunter liegende Schicht zu übertragen. Die Kunst ist, dass man selten alles entfernen will — man möchte ein bestimmtes Material schnell abtragen und dabei auf einem anderen stoppen. Diese Eigenschaft heißt Selektivität und erklärt, warum Leading‑Edge‑Fabs so viel in Ätzprozess‑Know‑how investieren (und warum Hersteller wie Lam Research Jahre in dessen Feinabstimmung investieren).

Ein moderner Stack kann Silizium, Siliziumoxid, Siliziumnitrid, Metalle und Hardmasks enthalten. Beim Ätzen muss oft eine Schicht sauber entfernt werden, während die „Ätzstopp“-Schicht intakt bleibt. Schlechte Selektivität kann kritische Schichten ausdünnen, Transistormaße verschieben oder Leckpfade erzeugen, die die Ausbeute senken.

Die meisten fortgeschrittenen Ätze verwenden ein Plasma: ein niedrigdruckiges Gas, das in reaktive Spezies energisiert wird.

Zwei Dinge passieren gleichzeitig:

Das Gleichgewicht zu halten ist die Kunst: zu viel Chemie kann Unterfressen verursachen; zu viel Ionenenergie kann das Gewünschte beschädigen.

Prozessteams verfolgen in der Regel einige Ergebnisse:

Selbst wenn das Rezept „richtig“ ist, wehren sich reale Wafer:

An führenden Nodes entscheidet das Management dieser Details oft darüber, ob etwas ein Labordemo bleibt oder in die Massenfertigung geht.

Wenn man an Skalierung denkt, stellt man sich oft eine einzige bahnbrechende Maschine vor, die immer kleinere Linien „druckt“. In der Praxis wird Musterübertragung durch die ganze Kette begrenzt — Resist, Hardmasks, Ätzselektivität, Schichtspannung und Reinigung — nicht durch ein einzelnes magisches Werkzeug.

Photoresist eignet sich gut zum Erfassen eines Musters, ist aber meist zu dünn und zu fragil, um den tiefen, präzisen Ätzen in modernen Devices zu widerstehen. Daher bauen Fabs Hardmask‑Stacks — sorgfältig gewählte Filme, die auf der Zielschicht aufgebracht werden.

Ein vereinfachter Ablauf:

Jede deponierte Schicht wird nicht nur nach dem Material ausgewählt, sondern danach, wie sie sich beim nächsten Ätzen verhält: wie schnell sie im Vergleich zu benachbarten Schichten ätzt, wie viel Rauheit sie erzeugt und wie gut sie ihre Form hält.

Wenn kritische Abmessungen kleiner werden, als ein einzelner Lithographie‑Durchgang zuverlässig definieren kann, nutzen Fabs Multi‑Patterning — das Zerlegen eines dichten Musters in mehrere Belichtungen und Übertragungen. Das fügt nicht nur Lithographie‑Schritte hinzu; es vervielfacht die unterstützenden Deposition/Etch‑Schleifen für Spacer, Mandrels, Trims und Cut‑Masks.

Die Konsequenz: das „Muster“ eines Leading‑Edge‑Chips ist oft das Ergebnis mehrerer Zyklen von Auftragen und Wegätzen mit strenger Kontrolle.

Weil jeder Schritt die Startbedingungen für den nächsten verändert, erzielen die besten Ergebnisse durch das Abstimmen der gesamten Sequenz — Materialien, Plasmabedingungen, Kammerreinheit und Reinigungen — als ein System. Eine kleine Verbesserung in einem Ätzschritt kann durch die nächste Deposition aufgehoben (oder verstärkt) werden, weshalb Prozessintegrations‑Know‑how über die Zeit zum Differenzierungsmerkmal wird.

Planare Transistoren waren überwiegend „flach“, was viele Schritte zu Malen und Beschnitzen einer Oberfläche machte. Das Skalieren trieb die Industrie in die dritte Dimension: zuerst FinFETs (ein vertikaler „Fin“, der vom Gate umschlossen wird), und jetzt Gate‑All‑Around (GAA)‑Konzepte, bei denen das Gate den Kanal vollständig umschließt (oft als gestapelte Nanosheets).

Sobald Features Seitenwände, Ecken und tiefe Kavitäten haben, ist Deposition kein einfaches „Top‑Coat“ mehr. Filme müssen konform sein — nahezu die gleiche Dicke am Boden eines Grabens wie an der oberen Oberfläche.

Deshalb gewinnen Verfahren wie ALD und fein abgestimmte CVD‑Schritte an Bedeutung: wenige Atome zu dünn an einer Seitenwand können höheren Widerstand, schlechtere Zuverlässigkeit oder eine schwache Barriere verursachen, die Materialdiffusion ermöglicht.

Ätzen muss das richtige Profil erzeugen: gerade Wände, saubere Böden, minimale Rauheit und selektive Entfernung eines Materials, ohne die darunter liegende Schicht anzufressen. In dichten 3D‑Mustern kann schon ein kleiner „Over‑Etch“ kritische Bereiche anritzen, während „Under‑Etch“ Rückstände hinterlässt, die spätere Deposition blockieren.

Viele moderne Strukturen haben ein hohes Seitenverhältnis — sehr tief gegenüber der Breite. Gleichmäßige Ergebnisse über Milliarden dieser Features zu erzielen ist schwierig, weil Reaktanten, Ionen und Nebenprodukte nicht gleichmäßig hinein‑ und hinausbewegt werden. Probleme wie Microloading und Seitenwand‑Schädigung werden wahrscheinlicher.

GAA und fortgeschrittene Interconnects bringen komplexere Materialstapel und ultradünne Grenzflächen. Das erhöht die Anforderungen an die Oberflächenvorbereitung: Pre‑Cleans, schonende Plasmabehandlungen und Grenzflächenkontrolle vor der nächsten Deposition. Wenn die „Oberfläche“ nur wenige atomare Lagen dick ist, wird Prozess‑Know‑how zum Unterschied zwischen einem funktionierenden Bauteil und einem, das später stillschweigend ausfällt.

„Ausbeute“ ist einfach der Anteil der Chips auf einem Wafer, die wie vorgesehen funktionieren. Wenn ein Wafer Tausende von Dies enthält, kann eine winzige Änderung in der Defektrate Hunderte mehr verkaufbarer Teile bedeuten. Deshalb fixieren Hersteller Zahlen, die klein klingen — bei großem Volumen werden kleine Verbesserungen zu realem Output.

Viele Ausbeuteverluste sind unter dem Mikroskop unspektakulär; sie zeigen sich als elektrische Fehler. Einige typische Beispiele:

Deposition‑ und Ätzschritte beeinflussen all diese Fälle. Ein Film, der leicht von der Zielvorgabe abweicht in Dicke, Zusammensetzung oder Uniformität, kann zwar „gut aussehen“, aber das Transistorverhalten so verschieben, dass Spezifikationen nicht mehr erreicht werden.

Selbst wenn kein offensichtlicher Defekt vorliegt, erzeugt Variation über den Wafer (oder von Wafer zu Wafer) Chips mit inkonsistentem Verhalten. Eine Ecke wird heißer, eine andere ist langsamer — plötzlich ändert sich die Produktklassifizierung oder das Teil fällt aus. Enge Kontrolle von Depositionraten, Plasmabedingungen und Ätzselektivität reduziert diese Schwankungen.

Moderne Fabs justieren Prozesse nicht nach Gefühl. Sie verlassen sich auf Metrologie (Messung von Dicke, kritischen Abmessungen, Profilen, Uniformität) und Inspektion (Partikel, Musterdefekte, Kantenprobleme). Die Ergebnisse fließen in Prozessanpassungen ein:

In der Praxis wird daraus auch ein Softwareproblem: Daten von Werkzeugen, Metrologie und Inspektion zusammenzuführen, damit Ingenieure schnell handeln können. Teams bauen oft interne Dashboards, Alarmierungen und „Was hat sich geändert?“-Tools, um die Schleife vom Signal zur Korrektur zu verkürzen. Plattformen wie Koder.ai helfen hier, indem sie Prozess‑ und Datenteams erlauben, leichte Web‑Apps aus Gesprächen heraus zu erstellen — nützlich, um Ausbeute‑KPIs, Ausreißer‑Notizen und Laufhistorien zu integrieren, ohne auf lange traditionelle Entwicklungszyklen warten zu müssen.

Das wertvollste Know‑how ist inkrementell: jeder Node lehrt, welche Ursachen bestimmte Defekte haben, welche Einstellungen mit der Zeit driften und welche Kombinationen stabil sind. Diese Lektionen tragen weiter — so startet der nächste Node mit einem besseren Playbook, nicht mit einem leeren Blatt.

Ein Depositions‑ oder Ätzwerkzeug läuft nicht mit einer einzigen „Einstellung“. Es läuft mit einem Rezept — einer strukturierten Abfolge von Schritten, die definiert, wie der Prozess zeitlich abläuft. Ein Rezept kann mehrere Phasen enthalten (Stabilisierungsphase, Pre‑Clean, Hauptschritt, Nachbehandlung), jede mit eigenen Gasflüssen, Druck, Temperatur, RF‑Leistung, Zeiten und Endpunkt‑Logik. Es beinhaltet auch die „stillen“ Details: Spülzeiten, Wafer‑Handling‑Verhalten und wie die Kammer vor dem ersten Wafer vorbereitet wird.

Mit dem Übergang zu neuen Nodes führen Fabs neue Materialien und 3D‑Geometrien ein — oft gleichzeitig. Ein Film, der auf einer flachen Oberfläche funktionierte, kann sich in tiefen, engen Features anders verhalten. Ein Ätzschritt, der in der vorigen Generation selektiv genug war, kann anfangen, eine neu eingeführte Liner‑ oder Barriereschicht zu beschädigen.

Deshalb entwickeln sich Rezepte: Gerätetargets verschieben sich (Geschwindigkeit, Energieverbrauch, Zuverlässigkeit), Geometrien werden enger und Integrationsanforderungen nehmen zu. Prozessentwicklung wird zu einem lang laufenden Zyklus von Feinanpassungen, Messen und erneuter Feinanpassung — manchmal zur Lösung von Problemen, die erst nach Tausenden von Wafern auftreten.

In der Hochvolumenfertigung reicht es nicht, dass eine Kammer einmal gute Ergebnisse liefert. Wiederholbarkeit bedeutet, dass dasselbe Rezept dieselben Ergebnisse Wafer für Wafer liefert. Tool‑zu‑Tool‑Matching bedeutet, dass ein Rezept, das auf ein anderes Werkzeug (oder in eine andere Fab) übertragen wird, weiterhin Dicke, Profil und Uniformität innerhalb enger Toleranzen erreicht — sonst leiden Produktion und Ausbeute.

Kontaminationskontrolle ist Teil dieser Realität. Kammern „altern“, wenn sich Filme auf internen Oberflächen aufbauen und Plasma‑Bedingungen sowie Partikelrisiko verändern. Fabs verlassen sich auf Kammerkonditionierung, Einlauf‑Runs, Reinigungen und präventive Wartungspläne, damit Prozesse über Monate stabil bleiben. Dieses operative Know‑how — wie Rezepte über Monate, nicht nur Minuten, performant bleiben — ist ein Bereich, in dem Erfahrung sich auszahlt.

Leading‑Edge‑Chips werden nicht einfach dadurch hergestellt, dass man ein Werkzeug kauft, es installiert und auf „Run“ drückt. Deposition‑ und Etch‑Schritte sind eng gekoppelt an das Chiplayout, den Materialstapel und die Zuverlässigkeitsziele, sodass die Personen, die die Ausrüstung bauen, und die, die die Fab betreiben, zusammen iterieren.

Chipdesigner definieren die benötigten Strukturen (z. B. kleinere Kontakte, höhere Vias, neue Metallstapel). Prozessintegrations‑Teams in der Fab übersetzen dieses Design in einen Schritt‑für‑Schritt‑Flow: diese Schicht deponieren, mustern, ätzen, reinigen, wiederholen. Werkzeughersteller wie Lam Research helfen dann, diese Anforderungen in in der Praxis herstellbare Rezepte auf realer Hardware zu überführen.

Diese Übergabe wird schnell zu einer Schleife: frühe Läufe zeigen Probleme (Profildrift, Rückstände, Linienkantensprödigkeit, unerwartete Schäden) und das Feedback fließt zurück in den Prozessfluss und die Werkzeugeinstellungen — manchmal sogar in Hardware‑Optionen wie Kammermaterialien, Plasmquellen oder Gaszuführung.

An der Spitze kann man Deposition oder Etch nicht isoliert optimieren, weil jeder Schritt die Startbedingungen des nächsten verändert. Eine kleine Änderung in Filmdichte kann die Ätzrate ändern; ein aggressiveres Ätzen kann nachfolgende Depositionen weniger konform machen. Ko‑Optimierung richtet aus:

Fabs balancieren konstant Durchsatz vs. Präzision: schnellere Verarbeitung kann Variabilität erhöhen, während extrem enge Kontrolle die Wafer‑Pro Stunde reduziert. Ebenso ist Selektivität vs. Schaden eine wiederkehrende Spannung: ein stark selektiver Ätzprozess kann härtere Bedingungen erfordern, die Rauheit oder Defektivität riskieren.

Ein zentraler Wertbestandteil ist fortlaufende Integrationsunterstützung — Vor‑Ort‑Troubleshooting, Matching der Leistung über Kammern hinweg, Reduktion von Ausreißern und schnelle Hilfe bei Ausbeutebewegungen. Für die Hochvolumenfertigung kann diese Partnerschaft genauso viel zählen wie das Datenblatt des Werkzeugs.

„Akkumulieren“ in der Chipherstellung bedeutet nicht nur, bessere Werkzeuge zu kaufen. Es beschreibt, wie kleine, praktische Vorteile sich aufsummieren, wenn Teams wiederholt dieselben Prozessklassen — Deposition und Etch — über mehrere Technologie‑Generationen laufen.

In diesem Sinne ist das Akkumulieren das Schwungrad aus:

Das garantiert keinen Erfolg, verkürzt aber in der Regel die Zeit vom „funktioniert im Demo“ zum „funktioniert täglich in der Produktion".

Wenn eine Fab einen neuen Node ramp‑t, trifft sie auf vorhersehbare Herausforderungen: Variabilität, Defekte, Randfälle und Tool‑zu‑Tool‑Matching. Jedes gelöste Problem erzeugt wiederverwendbares Wissen — wie man Plasmabedingungen so einstellt, dass empfindliche Schichten nicht beschädigt werden, welche Kammerreinigungen Partikelspikes verhindern oder wie man Drift erkennt, bevor sie sich als Ausbeuteverlust zeigt.

Mit der Zeit machen diese Lernschleifen spätere Ramp‑Projekte glatter. Teams starten näher am Ziel, weil sie viele der Sackgassen bereits kartiert haben.

Auch wenn ein anderer Ansatz auf dem Papier ähnlich aussieht, ist das Wechseln teuer und riskant:

Deshalb bleibt Fertigungs‑Know‑how oft erhalten und baut weiter aufeinander auf: ist ein Prozessfluss stabil, tendiert man dazu, ihn zu verfeinern — nicht neu zu starten — außer die Vorteile einer Änderung sind klar größer als die Wiederlern‑Kosten.

Ein Depositions‑ oder Ätzwerkzeug kann auf dem Papier fantastisch aussehen — bis es 24/7 Tausende Wafer mit konstanten Ergebnissen fahren muss. In der Hochvolumenfertigung sind Zuverlässigkeit und Laufzeit keine Luxusmerkmale. Sie bestimmen direkt, wie viele gute Wafer eine Fab ausliefern kann.

Deposition und Etch leben und sterben mit Prozessstabilität. Kleine Drifts in Gasflüssen, Kammerdruck, Plasmaleistung oder Temperatur können Filmdicke, Seitenwandwinkel oder Schadensniveaus verschieben — und ein funktionierendes Rezept in Ausbeuteverlust verwandeln.

Deshalb investieren führende Werkzeuge (inklusive Systeme von Lam Research) stark in wiederholbare Hardware: stabile RF‑Lieferung, präzise Massenstromregelung, Thermomanagement und Sensorik, die Exkursionen früh erkennt.

Selbst bei perfektem Prozess leidet die Produktion, wenn Werkzeuge häufig ausfallen. Reale Fabrikausbeute wird geprägt von:

Ein leichter zu wartendes Werkzeug — unterstützt von verlässlicher Ersatzteilplanung — hält mehr Kammern in Betrieb und mehr Chargen in Bewegung.

Höhere Laufzeit senkt typischerweise die Kosten pro Wafer: weniger Leerlauf bei Bedienern, bessere Auslastung teurer Reinraumsfläche und weniger Zeitverlust durch Nacharbeit. Ebenso macht konsistente Verfügbarkeit Lieferpläne vorhersehbar, was wichtig ist, wenn nachgelagerte Schritte eng getaktet sind.

Noch eine Realität: die Skalierung von Labordemos zur Massenproduktion belastet Werkzeuge anders. Längere Läufe, höhere Waferstarts und strengere Defektbudgets decken Schwachstellen schnell auf — daher wird Reliability‑Engineering Teil der Prozessfähigkeit.

Wenn Chips in kleinere Nodes und komplexere 3D‑Strukturen vorstoßen, hängt Fortschritt zunehmend davon ab, Deposition‑ und Etch‑Schritte mit extremer Präzision zu wiederholen — oft hunderte Male in einem Device‑Stapel. Der „nächste Engpass“ ist selten ein einzelner Durchbruch, sondern die kumulative Schwierigkeit, jeden Zyklus konsistent zu halten, dabei Ausbeute und Variabilität zu kontrollieren und Prozesse schnell genug hochzufahren, um der Nachfrage zu entsprechen.

Mehrere Trends werden Deposition/Etch besonders belasten:

Beim Vergleich von Werkzeugsuppliers oder Fab‑Ansätzen (einschließlich Lam Research und Wettbewerbern) auf Ergebnisse achten:

Für tiefergehende Erklärungen besuchen Sie verwandte Beiträge auf /blog. Wenn Sie Optionen bewerten — oder interne Tools bauen wollen, um Ausbeute, Ausreißer und Ramp‑Metriken zu analysieren — sehen Sie /pricing für unsere Betrachtungen zu Kosten, Geschwindigkeit und Fähigkeiten (inklusive wann eine Build‑with‑Chat‑Plattform wie Koder.ai traditionelle, langsame Softwareprozesse ersetzen kann).

Deposition ist der „Hinzufügen“-Schritt: Werkzeuge legen ultradünne Schichten ab (Metalle, Dielektrika, Barrieren, Liner, Hardmasks). Etch ist der „Entfernen“-Schritt: Werkzeuge tragen selektiv Material ab, um Muster zu übertragen und Strukturen zu formen.

Die Skalierung hängt davon ab, Dicke, Form und Grenzflächen im Nanometerbereich zu kontrollieren. Daher beeinflussen Qualität von Deposition und Etch direkt Leistung und Ausbeute.

„Leading‑Edge“ meint üblicherweise die fortschrittlichsten Nodes in der volumenstarken Produktion, wo Gerätearchitekturen und Materialien neu sind und Toleranzen sehr eng sind.

Es ist weniger ein Marketingbegriff und mehr die Realität enger Prozessfenster und hoher Empfindlichkeit gegenüber winzigen Abweichungen.

Weil moderne Chips durch wiederholte Zyklen gebaut werden:

Wenn Features kleiner und Schichtstapel komplexer werden, erfordert ein einzelnes „Layer“ oft , um die gewünschten Dimensionen und Profile zu erreichen.

Konformität beschreibt, wie gleichmäßig eine Schicht die Oberfläche, Seitenwände und den Boden einer 3D-Struktur bedeckt.

Sie ist wichtig, weil ungleichmäßige Beschichtung

Verfahren wie werden dort eingesetzt, wo hohe Konformität entscheidend ist.

Selektivität beschreibt, wie viel schneller ein Ätzprozess ein Material gegenüber einem anderen entfernt (häufig gegenüber einer Ätzstopp‑Schicht).

Hohe Selektivität hilft dabei:

Photoresist ist oft zu dünn und zu fragil für tiefe, präzise Ätzschritte. Ein Hardmask‑Stack fungiert als robusterer „Übersetzer“ zwischen dem Resist‑Muster und der darunterliegenden Schicht.

Typischer Ablauf:

Die Auswahl der Hardmask‑Materialien richtet sich nach .

Multi‑Patterning teilt ein dichtes Muster in mehrere Übertragungs‑Schritte auf, wenn eine einzelne Lithographie‑Belichtung den gewünschten Pitch nicht zuverlässig definiert.

Das fügt unterstützende Schritte wie Spacer‑ oder Mandrel‑Bildung hinzu und erhöht die Anzahl der benötigten Deposition+Etch‑Operationen (sowie Reinigungen und Metrologie), um ein finales Feature-Set zu erstellen.

Hochaspect‑Ratio‑Strukturen (sehr tief im Verhältnis zur Breite) erschweren den Transport:

Das erhöht das Risiko für Profilprobleme (Notching/Footing), Rückstände, Rauigkeit und Variabilität – daher werden Prozessanpassungen deutlich strenger.

Ausbeute ist der Anteil funktionsfähiger Dies auf einem Wafer. Deposition und Etch beeinflussen die Ausbeute, weil sie Defekte und Variabilität verursachen können, die sich elektrisch bemerkbar machen, z. B.:

Selbst kleine Drift in Dicke oder Profil können bei Leading‑Edge‑Dimensionen Geräte außerhalb der Spezifikation treiben.

Die Spezifikation eines Werkzeugs ist wichtig, aber in der Serienfertigung differenziert oft das Prozess‑Know‑how: Rezepte, Integrationssequenzen, Defekt‑Lernen und Tool‑Matching.

Dieses Know‑how akkumuliert, weil jede Node Erkenntnisse liefert über:

Deshalb sind Ausrüster wie strategisch wichtig für die führende Fertigung.