04 मई 2025·8 मिनट

लैम रिसर्च और चिप-निर्माण में संचयी लाभ

डिपोज़िशन और एट्च उपकरण लीडिंग-एज चिप्स को कैसे आकार देते हैं, क्यों प्रोसेस नो-हाउ समय के साथ संचयी होता है, और इसका यील्ड, नोड्स और स्केलिंग पर क्या असर होता है।

डिपोज़िशन और एट्च उपकरण लीडिंग-एज चिप्स को कैसे आकार देते हैं, क्यों प्रोसेस नो-हाउ समय के साथ संचयी होता है, और इसका यील्ड, नोड्स और स्केलिंग पर क्या असर होता है।

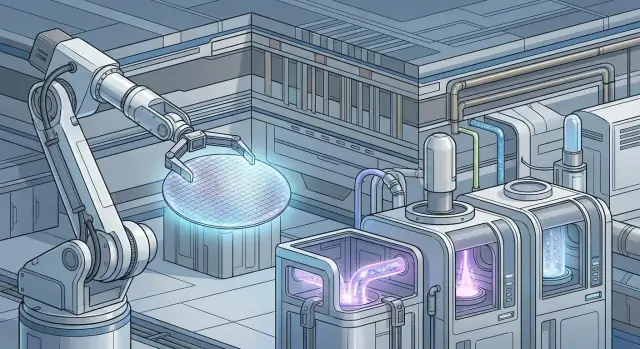

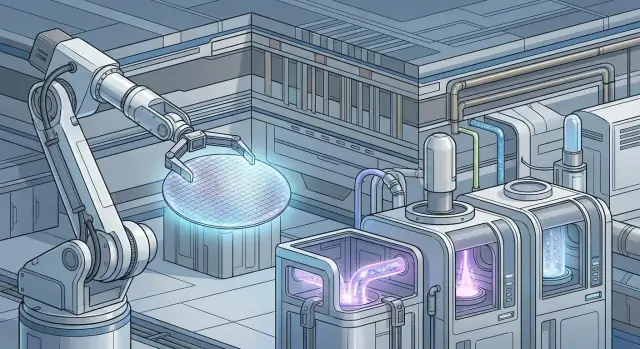

यदि आप चिपनिर्माण को उसके सबसे अधिक दोहराए जाने योग्य कदमों तक घटाते हैं, तो दो क्रियाएँ बार-बार दिखती हैं: डिपोज़िशन और एट्च।

डिपोज़िशन वह “जोड़ने” वाला कदम है। टूल वेफर पर अल्ट्रा-पतली फ़िल्में जमा करते हैं—कंडक्टर्स, इंसुलेटर्स, या विशेष बैरियर परतें—कभी-कभी बस कुछ परमाणुओं के स्तर पर। एट्च वह “हटाने” वाला कदम है। टूल चुनिंदा रूप से सामग्री हटाते हैं ताकि वे छोटे फीचर्स बनाएँ जो ट्रांजिस्टर और वायरिंग बनते हैं, आदर्श रूप से नीचे की परतों को नुकसान पहुँचाए बिना।

जैसे-जैसे चिप्स स्केल हुए हैं, ये दोनों कदम इंजीनियरों के लिए प्राथमिक नियंत्रण बन गए हैं ताकि नैनोमीटर मापदंडों पर सबसे ज़रूरी चीज़ों को नियंत्रित किया जा सके: मोटाई, आकार, और इंटरफ़ेसेस। इसीलिए उपकरण कंपनियाँ जैसे Lam Research लीडिंग-एज विनिर्माण के दिल के पास बैठती हैं।

“लीडिंग-एज” सामान्यत: सबसे उन्नत, उच्च-वॉल्यूम उत्पादन नोड्स को संदर्भित करता है—जहाँ डेंसिटी, पावर, और परफॉर्मेंस लक्ष्य सबसे आक्रामक होते हैं, और त्रुटि के लिए गुंजाइश न्यूनतम। यह सिर्फ मार्केटिंग संख्या नहीं है; यही वो जगह है जहाँ नए डिवाइस स्ट्रक्चर और नए मटेरियल सबसे पहले दिखते हैं।

टूल क्षमता मायने रखती है (यूनिफॉर्मिटी, सेलेक्टिविटी, डैमेज कंट्रोल, थ्रूपुट)। लेकिन प्रोसेस नो-हाउ उतना ही महत्वपूर्ण है: रेसिपीज़, इंटीग्रेशन ट्रिक्स, मीट्रॉली फीडबैक, और दोष-सीख जो एक शानदार टूल को एक स्थिर, उच्च-यील्ड फैक्ट्री प्रोसेस में बदल देते हैं।

यह लाभ टेक्नोलॉजी पीढ़ियों के साथ संचयी रूप से बढ़ता है क्योंकि हर नया नोड शून्य से नहीं शुरू होता—यह पहले की सीख पर बनता है कि फिल्में कैसे बढ़ती हैं, प्लाज़्मा कैसे व्यवहार करते हैं, और छोटे परिवर्तन कैसे बड़े यील्ड झूलों को जन्म देते हैं।

यह देखने के लिए कि डिपोज़िशन और एट्च चक्र क्यों लगातार बढ़ते रहते हैं, हम देखेंगे:

आधुनिक चिप को सिलिकॉन के ब्लॉक से “मशीन” नहीं किया जाता। इसे असेंबल किया जाता है—एक सूक्ष्म परत-केक की तरह—बार-बार अल्ट्रा-पतली फ़िल्में जोड़कर, उन्हें पैटर्न करके, और जिस चीज़ की ज़रूरत नहीं है उसे चुनिंदा रूप से हटाकर। यह प्रक्रिया सैकड़ों बार दोहराएँ, और आप ट्रांजिस्टर, वायरिंग, और इंसुलेटिंग बैरियर्स के साथ 3D में स्टैक्ड और इंटरट्वाइंड डिवाइस प्राप्त करते हैं।

ऊपर के स्तर पर, चिपनिर्माण एक परिचित ताल पर साइकिल करता है:

हर लूप अंतिम डिवाइस का एक “स्लाइस” बनाता है—गेट स्ट्रक्चर्स, संपर्क छेद, या इंटरकनेक्ट लाइन्स—जब तक चिप का लॉजिक और मेमोरी स्टैक से उभर कर नहीं आता।

जब फीचर्स सिंगल-डिजिट नैनोमीटर में मापे जाते हैं, तो मोटाई और आकार नियंत्रण केवल “अच्छा होना” नहीं रह जाता। एक परत जो थोड़ी मोटी है वह संकरे उद्घाटन को पिन्च कर सकती है; एक एट्च जो थोड़ी ज़्यादा आक्रामक है वह लाइन को चौड़ा कर सकता है या नीचे की परत को छेड़ सकता है। यहां तक कि छोटे प्रोफ़ाइल परिवर्तन—साइडवॉल एंगल, कॉर्नर राउंडिंग, सतह की खुरदरापन—बिजली के प्रवाह को बदल सकते हैं।

मैन्युफैक्चरिंग को प्रोसेस स्टेप्स (विशिष्ट डिपोज़िशन/एट्च ऑपरेशन्स) में संगठित किया जाता है जिन्हें एक प्रोसेस विंडो के भीतर चलाना चाहिए—वह सेटिंग्स की सीमा जहाँ परिणाम लगातार स्वीकार्य होते हैं। जैसे-जैसे चिप्स डेंस होते जाते हैं, वे विंडोज़ सिकुड़ती हैं। और क्योंकि बाद की परतें पहले परतों पर बनती हैं, एक छोटा विचलन मिसअलाइनमेंट, शॉर्ट्स, ओपन, और अंततः कम यील्ड में बदल सकता है।

डिपोज़िशन चिपनिर्माण का “सामग्री जोड़ने” वाला आधा है: एक वेफर पर अल्ट्रा-पतली परतें बनाना ताकि बाद के चरण पैटर्न, सुरक्षा, या नीचे की चीज़ों को इलेक्ट्रिकली अलग कर सकें। ये परतें सजावटी नहीं हैं—हर एक का एक विशिष्ट काम होता है, और उसे अरबों छोटे फीचर्स में विश्वसनीय रूप से काम करना चाहिए।

केमिकल वेपोर डिपोज़िशन (CVD) प्रतिक्रियाशील गैसों का उपयोग करता है जो वेफर सतह पर ठोस फ़िल्म बनाती हैं। यह कई डायलेक्ट्रिक और कुछ कंडक्टिव लेयर्स के लिए व्यापक रूप से उपयोग होता है क्योंकि यह बड़े क्षेत्रों को कुशलता से और अच्छी यूनिफॉर्मिटी के साथ कवर कर सकता है।

फिजिकल वेपोर डिपोज़िशन (PVD) (अक्सर “स्पट्टरिंग”) लक्ष्य सामग्री से एटमों को हटाकर उन्हें वेफर पर जमा करता है। PVD धातुओं और हार्डमास्क सामग्री के लिए आम है, विशेषकर जब आप घनी फ़िल्म चाहते हैं—लेकिन यह बहुत गहरे, संकरे स्ट्रक्चर्स की साइडवॉल्स को कोट करने में संघर्ष कर सकता है।

एटॉमिक लेयर डिपोज़िशन (ALD) एक सतह-सीमित प्रतिक्रिया के जरिए एक मॉलिक्युलर “डोज़” के रूप में सामग्री जमा करता है। यह धीमा है, लेकिन नियंत्रण और कवरेज तब ज़रूरी होते हैं जब गति से अधिक महत्व होता है—खासकर सबसे टाइट 3D फीचर्स में।

जैसे-जैसे चिप्स फिन्स, ट्रेंचेस, और वर्टिकल होल में चले गए, डिपोज़िशन एक साधारण “ऊपर रंगो” समस्या रहना बंद हो गया। कॉनफॉर्मैलिटी बताती है कि फ़िल्म कितनी समान रूप से फीचर की ऊपरी सतह, साइडवॉल और तल को कवर करती है।

यदि किसी परत की साइडवॉल पर पतली परत रह जाती है या खुले हिस्से पर पिन्च ऑफ़ हो जाती है, तो इलेक्ट्रिकली लीकिज़, खराब भराव, या बाद की एट्च स्टेप्स में असफलताएँ हो सकती हैं। गहरे, संकरे फीचर्स के लिए उच्च कॉनफॉर्मैलिटी निर्णायक है जहाँ त्रुटि की गुंजाइश बहुत कम होती है।

भले ही मोटाई सही हो, फ़िल्म को कई व्यावहारिक आवश्यकताओं को भी पूरा करना चाहिए:

लीडिंग-एज पर, डिपोज़िशन सिर्फ “एक फ़िल्म जोड़ना” नहीं है। यह सटीक सामग्री इंजीनियरिंग है, ताकि हर बाद की एट्च और पैटर्न स्टेप पूर्वानुमेय तरीके से व्यवहार करे।

एट्च चिपनिर्माण का “घटाने वाला” आधा है: एक फ़िल्म जमा होने और रिसिस्ट से पैटर्न किए जाने के बाद, एट्च खुले हुए सामग्री को हटाकर उस पैटर्न को नीचे की परत में ट्रांसफ़र करता है। चाल यह है कि आप शायद ही कभी सब कुछ हटाना चाहते हैं—बदल में आप चाहेंगे कि एक विशिष्ट सामग्री जल्दी हटे जबकि दूसरी परत पर रुक जाए। इस गुण को सेलेक्टिविटी कहा जाता है, और यही कारण है कि लीडिंग-एज फैब एट्च प्रोसेस नो-हाउ में इतना निवेश करते हैं (और Lam Research जैसे टूल विक्रेता वर्षों से इसे परिष्कृत करते हैं)।

आधुनिक स्टैक में सिलिकॉन, सिलिकॉन ऑक्साइड, सिलिकॉन नाइट्राइड, धातुएँ, और हार्डमास्क शामिल हो सकते हैं। एट्च के दौरान आपको एक लेयर को साफ़-सुथरा हटाने की आवश्यकता हो सकती है जबकि “एट्च स्टॉप” लेयर को बरकरार रखना होता है। खराब सेलेक्टिविटी से महत्वपूर्ण परतें पतली हो सकती हैं, ट्रांजिस्टर डायमेंशन्स बदल सकते हैं, या लीकज पाथ बन सकते हैं जो यील्ड को हानि पहुँचाते हैं।

अधिकतर उन्नत एट्च एक प्लाज़्मा का उपयोग करते हैं: एक कम-दबाव गैस को सक्रिय करके प्रतिक्रियाशील स्पीशीज़ बनाया जाता है।

एक साथ दो चीजें होती हैं:

इनका संतुलन कल है: बहुत ज्यादा कैमिस्ट्री फीचर को अंडरकट कर सकती है; बहुत अधिक आयन ऊर्जा उस चीज़ को नुकसान पहुँचा सकती है जिसे आप रखना चाहते हैं।

प्रोसेस टीमें आमतौर पर कुछ परिणाम पीछा करती हैं:

भले ही रेसिपी “सही” हो, असली वेफर्स प्रतिरोध करते हैं:

लीडिंग नोड्स पर, इन विवरणों का प्रबंधन अक्सर लैब डेमो और हाई-वॉल्यूम मैन्युफैक्चरिंग के बीच का अंतर होता है।

जब लोग चिप स्केलिंग की कल्पना करते हैं, तो अक्सर वे एक सिंगल ब्रेकथ्रू मशीन की कल्पना करते हैं जो कभी-smaller लाइनों को “प्रिंट” करती है। व्यवहार में, पैटर्न ट्रांसफ़र पूरी चेन—रिसिस्ट, हार्डमास्क, एट्च सेलेक्टिविटी, फिल्म स्ट्रेस, और क्लीनिंग—द्वारा प्रतिबंधित है, न कि किसी एक जादुई टूल द्वारा।

फोटोरेज़िस्ट पैटर्न कैप्चर करने में अच्छा है, लेकिन अक्सर यह बहुत पतला और नाज़ुक होता है ताकि आधुनिक डिवाइसों के लिए आवश्यक गहरे, सटीक एट्च सहन कर सके। इसलिए फैब हार्डमास्क स्टैक्स बनाते हैं—सावधानीपूर्वक चुनी गई परतें जो लक्ष्य परत के ऊपर जमा की जाती हैं।

सरल प्रवाह का रूप:

हर जमा की गई फ़िल्म को केवल उसके प्रकार के कारण नहीं चुना जाता, बल्कि इसलिए भी कि वह अगली एट्च के दौरान कैसे व्यवहार करेगी: वह कितनी तेज़ी से मिटती है, कितना रफ़नेस बनाती है, और कितनी अच्छी तरह अपना आकार बनाए रखती है।

जब क्रिटिकल डायमेंशन्स एक ही लिथोग्राफी पास से विश्वसनीय रूप से परिभाषित नहीं हो पाते, तो फैब मल्टी-पैटरनिंग का उपयोग करते हैं—एक घनिष्ठ पैटर्न को कई एक्सपोज़र्स और ट्रांसफ़र्स में विभाजित करना। इसका मतलब केवल अधिक लिथोग्राफी चरण नहीं है; यह स्पेसर्स, मॅन्ड्रल्स, ट्रिम्स, और कट मास्क के लिए सहायक डिपोज़िशन/एट्च लूप्स को गुणा करता है।

निष्कर्ष: लीडिंग-एज चिप पर जो “पैटर्न” है वह अक्सर कई चक्रीय डिपोज़िशन और एट्च के परिणाम के रूप में उभरता है।

क्योंकि हर स्टेप अगले के लिए प्रारंभिक स्थितियाँ बदल देता है, सर्वोत्तम परिणाम पूरे अनुक्रम—सामग्री, प्लाज़्मा कंडीशंस, चैम्बर क्लीनलिनेस, और क्लीन—को एक सिस्टम के रूप में ट्यून करने से आते हैं। एक छोटे से एट्च सुधार को अगली डिपोज़िशन द्वारा मिटाया (या बढ़ाया) जा सकता है, इसलिए प्रोसेस इंटीग्रेशन नो-हाउ समय के साथ एक महत्वपूर्ण भेद बन जाता है।

प्लेनर ट्रांजिस्टर ज्यादातर “फ्लैट” थे, जिससे कई स्टेप्स सतह पर रंगने और ट्रिम करने जैसा महसूस होता था। स्केलिंग ने इंडस्ट्री को 3D में धकेल दिया: पहले FinFETs (वर्टिकल “फिन” जिसे गेट घेरता है), और अब GAA (gate-all-around) अवधारणाएँ जहाँ गेट चैनल को पूरी तरह घेरता है (अक्सर स्टैक्ड नैनोशीट्स के रूप में)।

जब फीचर्स के पास साइडवॉल्स, कॉर्नर्स, और गहरे गुहा होते हैं, तो डिपोज़िशन एक साधारण “ऊपर कोट” नहीं रहती। फ़िल्में कॉनफॉर्मल होनी चाहिए—ट्रेंच के तल पर मोटाई लगभग उतनी ही होनी चाहिए जितनी ऊपर सतह पर।

इसीलिए ALD और सावधानीपूर्वक ट्यून किए गए CVD स्टेप्स लीडिंग-एज पर और भी अधिक महत्वपूर्ण होते हैं: साइडवॉल पर कुछ एटम कम पड़ना उच्च प्रतिरोध, खराब विश्वसनीयता, या कमजोर बैरियर में बदल सकता है जो मटेरियल को अनचाहे जगहों पर फैलने देता है।

एट्च को सही प्रोफ़ाइल बनानी होती है: सीधी दीवारें, साफ़ तले, न्यूनतम रफ़नेस, और एक मटेरियल को हटाते हुए दूसरे को बिना नुकसान पहुँचाए छोड़ना। घनी 3D पैटर्न में, थोड़ी सी भी “ओवर-एट्च” महत्वपूर्ण क्षेत्रों को नुक़सान पहुँचा सकती है, जबकि “अंडर-एट्च” अवशेष छोड़ देता है जो बाद की डिपोज़िशन को ब्लॉक कर देता है।

कई आधुनिक संरचनाएँ उच्च एस्पेक्ट रेशियो की होती हैं—गहराई में बहुत अधिक तुलना में संकीर्णता। इन अरबों फीचर्स में समान परिणाम प्राप्त करना कठिन है क्योंकि रिऐक्टेंट्स, आयन, और बायप्रोडक्ट्स टाइट स्पेस में समान रूप से नहीं आते-जाते। माइक्रोलोडिंग और साइडवॉल डैमेज जैसे समस्याएँ अधिक संभाव्य होती हैं।

GAA और एडवांस्ड इंटरकनेक्ट्स अधिक जटिल मटेरियल स्टैक्स और अल्ट्रा-पतले इंटरफेसेस लाते हैं। इससे सतह तैयारी की मांग बढ़ जाती है: प्री-क्लीन्स, सौम्य प्लाज़्मा ट्रीटमेंट्स, और अगली डिपोज़िशन से पहले इंटरफेस कंट्रोल। जब “सतह” सिर्फ कुछ एटॉमिक परतें मोटी है, तो प्रोसेस नो-हाउ उस डिवाइस के काम करने या बाद में धीरे-धीरे फेल होने के बीच का फर्क बन जाता है।

“यील्ड” बस वेफर पर काम करने वाले चिप्स का हिस्सा है। यदि एक वेफर में हजारों चिप्स हैं, तो दोष दर में छोटा परिवर्तन सैकड़ों अतिरिक्त बेचने योग्य हिस्सों में बदल सकता है। इसलिए निर्माता उन छोटी संख्याओं पर obsess करते हैं—क्योंकि स्केल पर छोटे सुधार वास्तविक आउटपुट बन जाते हैं।

कई यील्ड लॉसेज़ माइक्रोस्कोप के नीचे नाटकीय नहीं दिखते; वे इलेक्ट्रिक विफलताओं के रूप में उभरते हैं। कुछ सामान्य उदाहरण:

डिपोज़िशन और एट्च स्टेप्स इन सभी को प्रभावित कर सकते हैं। एक फ़िल्म जो मोटाई, संगठना, या यूनिफॉर्मिटी में थोड़ी सी भी भटकी हुई हो सकती है और फिर भी “ठीक” दिख सकती है, लेकिन वह ट्रांजिस्टर व्यवहार को इतना बदल सकती है कि वह स्पीड या पावर लक्ष्यों को मिस कर दे।

भले ही कोई स्पष्ट दोष न हो, वेफर में (या वेफर से वेफर) परिवर्तनशीलता ऐसे चिप्स बनाती है जो असंगत व्यवहार करते हैं। एक कोना अधिक गर्म चलता है, दूसरा कोना धीमा है, और अचानक प्रोडक्ट बिनिंग बदल जाती है—या भाग फेल हो जाता है। डिपोज़िशन दरों, प्लाज़्मा कंडीशंस, और एट्च सेलेक्टिविटी का कड़ा नियंत्रण इन उतार-चढ़ाव को कम करता है।

आधुनिक फैब प्रक्रियाओं को अंतर्ज्ञान से नहीं ट्यून करते। वे मीट्रॉली (मोटाई, क्रिटिकल डायमेंशन्स, प्रोफ़ाइल आकार, यूनिफॉर्मिटी मापना) और इंस्पेक्शन (कण, पैटर्न दोष, एज इश्यूज ढूँढना) पर निर्भर करते हैं। परिणाम प्रोसेस समायोजनों में फीडबैक करते हैं:

व्यवहार में, यह एक सॉफ्टवेयर समस्या भी बन जाती है: टूल, मीट्रॉली, और इंस्पेक्शन के डेटा को जोड़कर कुछ ऐसा बनाना जिस पर इंजीनियर जल्दी कार्रवाई कर सकें। टीमें अक्सर आंतरिक डैशबोर्ड, अलर्ट्स, और “क्या बदला?” टूल बनाती हैं ताकि सिग्नल से फ़िक्स तक का लूप छोटा हो सके। Koder.ai जैसी प्लेटफ़ॉर्म्स यहां मदद कर सकती हैं—प्रोसेस और डेटा टीमों को चैट से हल्के वेब ऐप्स जल्दी से बनाने देने में उपयोगी, जब लंबे पारंपरिक विकास चक्रों का इंतजार नहीं करना हो।

सबसे मूल्यवान नो-हाउ incremental होता है: हर नोड सिखाता है कि कौन से दोष पैदा करते हैं, कौन सी सेटिंग्स समय के साथ डिफ्ट होती हैं, और कौन से संयोजन stable हैं। ये सब सबक आगे बढ़ते हैं—तो अगला नोड एक बेहतर प्लेबुक के साथ शुरू होता है, खाली शीट के साथ नहीं।

एक डिपोज़िशन या एट्च टूल एक सिंगल “सेटिंग” पर नहीं चलता। यह एक रेसिपी पर चलता है—कदमों का संगठित अनुक्रम जो परिभाषित करता है कि प्रोसेस समय के साथ कैसे होता है। एक रेसिपी में कई चरण हो सकते हैं (स्थिरीकरण, प्री-क्लीन, मुख्य स्टेप, पोस्ट-ट्रीटमेंट), प्रत्येक का अपना गैस फ़्लो, प्रेशर, तापमान, RF पावर, समय, और एंडपॉइंट लॉजिक होता है। इसमें “शांत” विवरण भी होते हैं: पर्ज़ समय, वेफर हैंडलिंग व्यवहार, और चैम्बर कैसे पहले वेफर से पहले तैयार किया जाता है।

जैसे-जैसे चिप्स नए नोड्स की ओर बढ़ते हैं, फैब नए मटेरियल और नए 3D आकार पेश करते हैं—अक्सर एक साथ। एक फ़िल्म जो फ़्लैट सतह पर काम करती थी वह गहरे, संकरे फीचर्स पर अलग तरह से व्यवहार कर सकती है। एक एट्च स्टेप जो पिछली पीढ़ी पर पर्याप्त सेलेक्टिव था, वह किसी नए लाइनर या बैरियर को नुकसान पहुँचाने लगे।

इसलिए रेसिपीज़ विकसित होती हैं: डिवाइस लक्ष्य बदलते हैं (स्पीड, पावर, विश्वसनीयता), ज्योमेट्री तंग होती है, और इंटीग्रेशन सीमाएँ बढ़ती हैं। प्रोसेस डेवलपमेंट लगातार ट्यूनिंग, माप, और फिर से ट्यूनिंग का एक लंबा चक्र बन जाता है—कभी-कभी उन समस्याओं को हल करने के लिए जो केवल हजारों वेफर्स के बाद ही दिखाई देती हैं।

हाई-वॉल्यूम मैन्युफैक्चरिंग में, एक चैम्बर का एक बार अच्छा परिणाम देना पर्याप्त नहीं है। रिपीटेबिलिटी का अर्थ है कि वही रेसिपी वॉपर के बाद वही परिणाम देती है। टूल-टू-टूल मैचिंग का अर्थ है कि एक रेसिपी को दूसरे टूल (या दूसरे फैब) में ट्रांसफर करने पर वही मोटाई, प्रोफ़ाइल और यूनिफॉर्मिटी कड़े सीमाओं के भीतर बनी रहे—अन्यथा उत्पादन नियोजन और यील्ड प्रभावित होती है।

कंटामिनेशन कंट्रोल इस वास्तविकता का हिस्सा है। चैम्बर्स समय के साथ “एज” करते हैं क्योंकि अंदरूनी सतहों पर फिल्में जमा हो जाती हैं, जो प्लाज़्मा कंडीशंस और पार्टिकल रिस्क को प्रभावित करती हैं। फैब चैम्बर कंडीशनिंग, सीज़निंग रन, क्लीन और प्रिवेंटेटिव मेंटेनन्स शेड्यूल्स पर निर्भर करते हैं ताकि प्रोसेस महीनों तक स्थिर रहे, न कि मिनटों के लिए। यह ऑपरेशनल नो-हाउ—कैसे रेसिपीज़ को महीनों तक नहीं बल्कि लगातार प्रदर्शन में बनाए रखना—ही अनुभव है जो संचयी बनता है।

लीडिंग-एज चिप्स सिर्फ एक टूल खरीदकर, उसे इंस्टॉल करके, और “रन” दबाकर नहीं बनाए जाते। डिपोज़िशन और एट्च स्टेप्स चिप की लेआउट, मटेरियल स्टैक, और विश्वसनीयता लक्ष्यों से गहराई से जुड़े होते हैं, इसलिए उपकरण बनाने वाले और फैब चलाने वाले लोग साथ मिलकर इटरेट करते हैं।

चिप डिज़ाइनर वे संरचनाएँ परिभाषित करते हैं जो उन्हें चाहिए (उदा., छोटे संपर्क, ऊँचे वायस, नए मेटल स्टैक्स). फैब के अंदर प्रोसेस इंटीग्रेशन टीमें उस डिज़ाइन को स्टेप-बाय-स्टेप फ्लो में अनुवाद करती हैं: इस परत को डिपोज़िट करो, पैटर्न करो, एट्च करो, क्लीन करो, दोहराओ। फिर Lam Research जैसे टूल मेकर उन आवश्यकताओं को वास्तविक हार्डवेयर पर मैन्युफैक्चरेबल रेसिपीज़ में बदलने में मदद करते हैं।

हैंडऑफ जल्दी ही लूप बन जाता है: शुरुआती रन इश्यूज़ (प्रोफ़ाइल डिफ्ट, रेसिड्यू, लाइन-एज रफ़नेस, अनपेक्षित डैमेज) दिखाते हैं, और फीडबैक प्रोसेस फ्लो और टूल सेटिंग्स दोनों में वापस जाता है—कभी-कभी हार्डवेयर विकल्पों तक, जैसे चैम्बर सामग्रियाँ, प्लाज़्मा सोर्सेज, या गैस डिलीवरी।

लीडिंग-एज पर, आप डिपोज़िशन या एट्च को अलग से ऑप्टिमाइज़ नहीं कर सकते क्योंकि हर स्टेप अगले की प्रारंभिक स्थिति बदल देता है। छोटी सी फ़िल्म घनत्व में बदलाव एट्च दर बदल सकता है; एक ज़्यादा आक्रामक एट्च डाउनस्ट्रीम डिपोज़िशन को कम कॉनफॉर्मल बना सकता है। सह-अनुकूलन का लक्ष्य है:

फैब लगातार थ्रूपुट बनाम प्रिसिजन का संतुलन करते हैं: तेज प्रोसेसिंग वैरिएबिलिटी बढ़ा सकती है, जबकि अत्यंत कड़ा नियंत्रण वेफर्स पर घंटे घटा सकता है। इसी तरह, सेलेक्टिविटी बनाम डैमेज का तनाव बार-बार आता है: एक एट्च जो एक मटेरियल को प्राथमिकता देता है वह अक्सर कठोर कंडीशन्स मांगता है जो रफ़नेस या दोषिता का जोखिम पैदा कर सकते हैं।

एक महत्वपूर्ण मूल्य-संसाधन जारी इंटीग्रेशन सपोर्ट है—ऑन-साइट ट्रबलशूटिंग, चैम्बर के पार प्रदर्शन मैचिंग, एक्सकर्शन कम करना, और यील्ड मूव होने पर तेज़ रिकवरी में मदद करना। हाई-वॉल्यूम मैन्युफैक्चरिंग के लिए, यह साझेदारी टूल के स्पेक शीट जितनी ही महत्वपूर्ण हो सकती है।

एक डिपोज़िशन या एट्च टूल स्पेक शीट पर शानदार लग सकता है—जब तक उसे 24/7, हजारों वेफर्स पर, हर बार समान परिणाम देने के लिए चलाना न पड़े। हाई-वॉल्यूम मैन्युफैक्चरिंग में विश्वसनीयता और अपटाइम ‘अच्छा होने’ की चीजें नहीं हैं। वे सीधे निर्धारित करते हैं कि फैब कितने अच्छे वेफर्स भेज सकती है।

डिपोज़िशन और एट्च प्रोसेस स्थिरता पर जीवित रहते हैं। गैस फ्लोज़, चैम्बर प्रेशर, प्लाज़्मा पावर, या तापमान में छोटे-छोटे ड्रिफ्ट फिल्म मोटाई, साइडवॉल कोण, या डैमेज स्तर बदल सकते हैं—और काम कर रहे रेसिपी को यील्ड लॉस में बदल सकते हैं।

इसीलिए लीडिंग टूल (जिसमें Lam Research सिस्टम भी शामिल हैं) रिपीटेबल हार्डवेयर में भारी निवेश करते हैं: स्थिर RF डिलिवरी, सटीक मास फ्लो कंट्रोल, थर्मल मैनेजमेंट, और सेंसर जो एक्सकर्शन को जल्दी पकड़ सकें।

भले ही प्रक्रिया परफेक्ट हो, उत्पादन तब प्रभावित होता है जब टूल अकसर डाउन होते हैं। असली फैब आउटपुट निम्नसे प्रभावित होता है:

एक ऐसा टूल जो आसानी से सर्विस हो सके—और मजबूत स्पेयर्स फोरकास्टिंग द्वारा समर्थित हो—ज़्यादा चैम्बर्स चलाए रखता है और ज़्यादा लॉट्स आगे बढ़ाते रखता है।

ऊंचा अपटाइम आमतौर पर प्रति वेफर लागत घटाता है: कम_IDLE ऑपरेटर्स, महंगी क्लीनरूम स्पेस का बेहतर उपयोग, और रियवर्क में कम समय। उतना ही महत्वपूर्ण, लगातार उपलब्धता डिलिवरी शेड्यूल्स को पूर्वानुमेय बनाती है—जो तब मायने रखता है जब डाउनस्ट्रीम स्टेप्स कड़ी कतार में हों।

एक और वास्तविकता: लैब डेमो से मास प्रोडक्शन तक स्केल करना टूल्स को अलग तरह से दबाव में डालता है। विस्तारित रन, उच्च वेफर स्टार्ट्स, और कड़ा दोष बजट कमजोरियों को जल्दी उजागर करते हैं—इसलिए विश्वसनीयता इंजीनियरिंग “प्रोसेस कैपेबिलिटी” का कोर हिस्सा बन जाती है।

जैसे-जैसे चिप्स छोटे नोड्स और अधिक 3D स्ट्रक्चर्स की ओर जाते हैं, प्रगति अक्सर बार-बार डिपोज़िशन और एट्च स्टेप्स को अत्यधिक सटीकता से दोहराने पर निर्भर करती है—अक्सर एक डिवाइस स्टैक में सैकड़ों बार। “अगला बॉटलने</s>

डिपोज़िशन वह “जोड़ने” वाली क्रिया है: टूल वेफर पर अल्ट्रा-पतली परतें जमा करते हैं (धातु, डायलेक्ट्रिक, बैरियर, लाइनर, हार्डमास्क)। एट्च/इच वह “हटाने” वाली क्रिया है: टूल चुनिंदा रूप से सामग्री काटते हैं ताकि पैटर्न ट्रांसफ़र हो और फीचर बनें。

स्केलिंग इस बात पर निर्भर करती है कि नैनोमीटर पैमाने पर मोटाई, आकार और इंटरफ़ेस कितनी सटीक नियंत्रित की जाती हैं, इसलिए डिपोज़िशन/एट्च की गुणवत्ता सीधे प्रदर्शन और यील्ड को प्रभावित करती है।

“लीडिंग-एज” आमतौर पर सबसे उन्नत, उच्च-वॉल्यूम उत्पादन नोड्स को कहते हैं, जहाँ डेंसिटी, पावर और परफॉर्मेंस के लक्ष्य सबसे कड़े होते हैं और त्रुटि की गुंजाइश बहुत कम होती है।

यह सिर्फ मार्केटिंग नंबर नहीं है; यही वो जगह है जहाँ नए डिवाइस स्ट्रक्चर और नए मटेरियल सबसे पहले दिखाई देते हैं।

आधुनिक चिप कई बार दोहराए जाने वाले चक्रों पर बनती है:

जैसे-जैसे फीचर छोटे होते हैं और स्टैक्स जटिल होते हैं, एक परत को इच्छित आयाम और प्रोफ़ाइल तक पहुँचाने के लिए अक्सर चाहिए होते हैं।

कॉनफॉर्मैलिटी वह माप है कि कोई फ़िल्म 3D फीचर के ऊपर, साइडवॉल और नीचे को कितनी समान रूप से कवर करती है।

यह महत्वपूर्ण इसलिए है क्योंकि असमान कवरेज से:

जब कॉनफॉर्मैलिटी क्रिटिकल हो तो ALD जैसी तकनीकें अक्सर इस्तेमाल की जाती हैं।

सेलेक्टिविटी यह बताती है कि एक एट्च किसी मटेरियल को दूसरे की तुलना में कितनी तेज़ी से हटाता है (अक्सर एक ‘एट्च स्टॉप’ परत की तुलना में)।

उच्च सेलेक्टिविटी आपको मदद करती है:

फोटोरेज़िस्ट अक्सर आधुनिक एट्च की गहराई/प्रिसिजन सहन करने के लिए काफी पतला और नाजुक होता है। एक हार्डमास्क स्टैक कठोर ‘ट्रांसलेटर’ की तरह काम करता है जो रिसिस्ट पैटर्न को टार्गेट फिल्म तक स्थानांतरित करने में टिकाऊ रहता है।

साधारण फ्लो:

हार्डमास्क का चुनाव एट्च रेसिस्टेंस, सेलेक्टिविटी, और प्रोफ़ाइल कंट्रोल पर आधारित होता है।

मल्टी-पैटरनिंग उस स्थिति में उपयोग की जाती है जब एकल लिथो पास अंतिम पिच को विश्वसनीय रूप से परिभाषित नहीं कर सकता।

यह एक डेंस पैटर्न को कई पैटर्न-ट्रांसफ़र स्टेप्स में बाँट देता है, और इससे स्पेसर या मॅन्ड्रेल फॉर्मेशन जैसे सहायक चरण जुड़ते हैं। इसका मतलब है कि एक अंतिम फीचर सेट बनाने के लिए और भी अधिक डिपोज़िशन + एट्च ऑपरेशन्स (साथ ही क्लीन और मीट्रॉली) की आवश्यकता होती है।

हाई एस्पेक्ट रेशियो वाले फीचर्स (बहुत गहरे और अपेक्षाकृत संकरे) में ट्रांसपोर्ट कठिन हो जाता है:

नतीजा: प्रोफ़ाइल इश्यू (नॉचिंग/फूटिंग), रेसिड्यू, रफ़नेस और वैरिएबिलिटी का जोखिम बढ़ जाता है—इसलिए प्रोसेस ट्यूनिंग अधिक सख्त हो जाती है।

यील्ड वह हिस्सा है जो वेफर पर सही काम करने वाले चिप्स का बताता है। डिपोज़िशन और एट्च कई तरीकों से दोष और वैरिएबिलिटी को जन्म देते हैं जो इलेक्ट्रिकल फेल्यर बनते हैं, जैसे:

लीडिंग-एज डाइमेंशन्स पर भी “छोटी” मोटाई या प्रोफ़ाइल में ड्रिफ्ट डिवाइस को स्पेक से बाहर कर सकती है, इसलिए डिपोज़िशन और एट्च का प्रभाव सीधे यील्ड पर पड़ता है।

टूल के स्पेक्स मायने रखते हैं, लेकिन प्रोडक्शन में जो अंतर बनाता है वह अक्सर प्रोसेस नो-हाउ होता है: रेसिपीज़, इंटीग्रेशन सीक्वेंसिंग, दोष सीखना, और टूल-टू-टूल मैचिंग।

यह नॉलेज संचयी होती है क्योंकि हर नोड पिछली सीख पर बनता है—कैसे फिल्में जटिल टोपोग्राफी पर बढ़ती हैं, प्लाज़्मा प्रोफ़ाइल और डैमेज का व्यवहार, और कैसे चैम्बर को लंबे रन में स्टेबल रखा जाए।

इसी कारण से उपकरण कंपनियाँ जैसे Lam Research लीडिंग-एज विनिर्माण में रणनीतिक रूप से महत्वपूर्ण हो सकती हैं।

जब आप टूल वॉल्यूम में चलाते हैं, तो रिलेबलिटी और अपटाइम बहुत महत्वपूर्ण हो जाते हैं। छोटे-छोटे गैस फ्लो, चैम्बर प्रेशर, प्लाज़्मा पावर या तापमान के ड्रिफ्ट से फिल्म मोटाई, साइडवॉल एंगल या डैमेज स्तर बदल सकते हैं—जो एक काम करने वाले रेसिपी को यील्ड लॉस में बदल सकते हैं।

इसलिए टूल निर्माताएँ स्थिर हार्डवेयर, सटीक मास फ्लो कंट्रोल, थर्मल मैनेजमेंट और सेंसरिंग में निवेश करती हैं ताकि एक्सकर्शन जल्दी पकड़ा जा सके और अपटाइम बढ़े।

जैसे-जैसे नोड छोटे होते जा रहे हैं और और अधिक 3D संरचनाएँ आती जा रही हैं, डिपोज़िशन और एट्च चक्रों को सैकड़ों बार बेहद सटीकता से दोहराना आवश्यक होगा। अगला बॉटलनेक अक्सर कोई एक बड़ी खोज नहीं, बल्कि हर साइकिल को सुसंगत बनाए रखने, यील्ड और वैरिएबिलिटी कंट्रोल करने और नए प्रोसेस को तेजी से रैम्प करने की संयुक्त चुनौती होती है।

यदि आप टूल विक्रेता या फैब दृष्टिकोणों की तुलना कर रहे हैं, तो निचे वाले आउटकम्स पर ध्यान दें:

और गहराई में जाने के लिए /blog पर संबंधित स्पष्टीकरण पढ़ें। यदि आप विकल्पों का मूल्यांकन कर रहे हैं—या यील्ड, एक्सकर्शन और रैम्प मेट्रिक्स विश्लेषण के लिए आंतरिक टूलिंग बना रहे हैं—तो /pricing देखें, जहाँ हम लागत, गति और क्षमता के बारे में हमारी सोच साझा करते हैं (और जब Koder.ai जैसे चैट-आधारित प्लेटफ़ॉर्म एक धीमी लेगेसी सॉफ़्टवेयर पाइपलाइन की जगह ले सकते हैं)।