Perché deposizione ed etch stanno al centro della scalabilità dei chip

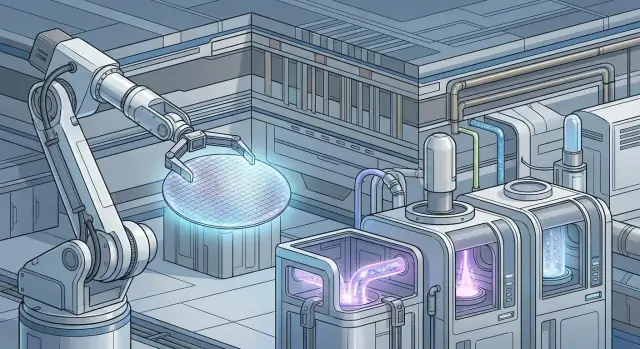

Se si riduce la produzione di chip ai gesti più ripetibili, due azioni ricorrono continuamente: deposizione ed etch.

Deposizione è il passo "aggiungi". Gli strumenti depositano film ultrasottili—conduttori, isolanti o strati barriera—su un wafer, a volte pochi atomi alla volta. Etch è il passo "rimuovi". Gli strumenti scolpiscono selettivamente il materiale per creare le piccole feature che diventano transistor e interconnessioni, idealmente senza danneggiare gli strati sottostanti.

Man mano che i chip sono scalati, questi due passaggi sono diventati le manopole principali che gli ingegneri usano per controllare ciò che conta a dimensioni nanometriche: spessore, forma e interfacce. Ecco perché aziende di equipment come Lam Research sono così vicine al cuore della produzione all'avanguardia.

Cosa significa davvero "leading-edge"

"Leading-edge" generalmente si riferisce ai nodi di produzione più avanzati e ad alto volume—dove densità, consumo energetico e prestazioni sono più aggressivi e il margine di errore è il più piccolo. Non è solo un numero di marketing; è dove nuove strutture di dispositivo e nuovi materiali compaiono per primi.

Il vantaggio composto

La capacità dello strumento conta (uniformità, selettività, controllo dei danni, throughput). Ma la conoscenza del processo conta altrettanto: le ricette, i trucchi di integrazione, il feedback metrologico e l'apprendimento sui difetti che trasformano uno strumento eccellente in un processo di fab stabile e ad alta resa.

Questo vantaggio si compone attraverso le generazioni tecnologiche perché ogni nuovo nodo non parte da zero—si basa sull'apprendimento precedente su come crescono i film, come si comportano i plasma e come piccole variazioni creano grandi oscillazioni di resa.

Cosa tratteremo dopo

Per capire perché i cicli di deposizione e etch si moltiplicano, vedremo:

- Patterning al limite e perché i loop ripetuti "deposit–etch–clean" sono comuni

- Strutture 3D (feature ad alto rapporto d'aspetto) più difficili da riempire e da incidere

- Apprendimento sulla resa, difetti e variabilità—dove l'esperienza paga

- Loop di feedback tra produttori di strumenti e fab che accelerano il miglioramento

Da strati a logica: come vengono effettivamente costruiti i chip moderni

Un chip moderno non viene "lavorato" da un blocco di silicio. È assemblato—più simile a una torta a strati microscopica—aggiungendo ripetutamente film ultrasottili, patternandoli e rimuovendo selettivamente ciò che non serve. Facendo questo centinaia di volte, si ottengono transistor, linee di interconnessione e barriere isolanti impilate e intrecciate in 3D.

Il loop ripetuto: aggiungi, patterna, rimuovi

A un alto livello, la produzione cicla attraverso un ritmo familiare:

- Deposizione deposita un film (metallo, ossido, nitruro e altro), spesso pochi atomi o pochi nanometri di spessore.

- Patterning definisce dove quel film deve rimanere (usando la litografia per creare una maschera).

- Etch rimuove le regioni esposte, trasferendo il pattern nel film.

Ogni loop crea una "fetta" del dispositivo finale—strutture di gate, fori di contatto o linee di interconnessione—finché la logica e la memoria del chip non emergono dallo stack.

Perché le feature piccolissime richiedono controllo estremo

Quando le feature si misurano in nanometri singoli, il controllo di spessore e forma smette di essere "bello da avere". Un film leggermente troppo spesso può chiudere un'apertura stretta; un etch troppo aggressivo può allargare una linea o danneggiare uno strato sottostante. Anche piccoli cambiamenti di profilo—angolo delle pareti laterali, arrotondamento degli angoli, rugosità superficiale—possono spostare come scorre l'elettricità.

Passaggi di processo, finestre di processo e resa

La produzione è organizzata in passaggi di processo (specifiche operazioni di deposizione/etch) che devono funzionare dentro una finestra di processo—l'intervallo di impostazioni in cui i risultati sono costantemente accettabili. Con l'aumento della densità, queste finestre si restringono. E poiché gli strati successivi si basano su quelli precedenti, una piccola deviazione può propagarsi in disallineamenti, cortocircuiti, aperture e, in ultima analisi, una resa inferiore.

Deposizione 101: mettere film con controllo a livello atomico

La deposizione è la metà "aggiungi materiale" della produzione: costruire film ultrasottili su un wafer in modo che i passaggi successivi possano patternare, proteggere o isolare elettricamente ciò che c'è sotto. Questi film non sono decorativi—ognuno è scelto per un compito specifico e deve funzionare in modo affidabile su miliardi di piccole feature.

I tre approcci principali: CVD, PVD e ALD

Chemical Vapor Deposition (CVD) usa gas reattivi che formano un film solido sulla superficie del wafer. È molto usata per molti dielettrici e alcuni strati conduttivi perché copre aree ampie in modo efficiente e con buona uniformità.

Physical Vapor Deposition (PVD) (spesso "sputtering") stacca atomi da un target e li deposita sul wafer. Il PVD è comune per metalli e materiali hardmask, specialmente quando si vuole un film denso—ma può avere difficoltà a rivestire le pareti laterali di strutture molto profonde e strette.

Atomic Layer Deposition (ALD) deposita materiale una "dose" molecolare alla volta tramite reazioni superficiali auto‑limitanti. È più lenta, ma eccelle quando il controllo e la copertura sono più importanti della velocità—particolarmente nelle feature 3D più critiche.

Con l'uso di fins, trincee e fori verticali, la deposizione ha smesso di essere un semplice problema di "verniciare la sommità". La conformalità descrive quanto uniformemente un film ricopre superficie superiore, pareti laterali e fondo di una feature.

Se uno strato è sottile sulla parete laterale o occlude l'apertura, si possono avere perdite elettriche, riempimenti scorretti o fallimenti nei successivi passaggi di etch. Un'alta conformalità è cruciale per feature profonde e strette dove il margine di errore è minimo.

Proprietà del film che possono determinare la resa

Anche se lo spessore è corretto, il film deve soddisfare diversi requisiti pratici:

- Uniformità: spessore coerente su tutto il wafer e da wafer a wafer.

- Impurità: atomi indesiderati possono alterare il comportamento elettrico o causare problemi di affidabilità.

- Stress: film troppo tensili o compressivi possono deformare strutture o creparsi.

- Aderenza: gli strati devono rimanere saldi attraverso cicli termici, pulizie ed etch.

Esempi intuitivi: cosa fanno realmente questi strati

- Liner rivestono le pareti laterali per proteggere le superfici e impostare le condizioni di partenza per i riempimenti successivi.

- Barriere impediscono ai metalli di diffondere nei materiali circostanti (critico per l'affidabilità).

- Hardmask funzionano come stencil resistenti che sopportano etch aggressivi meglio del photoresist.

- Strati dielettrici isolano elettricamente e separano i conduttori—essenziali per prevenire cortocircuiti.

All'avanguardia, la deposizione non è solo "aggiungere un film". È ingegneria dei materiali precisa, sintonizzata affinché ogni successivo passo di etch e pattern si comporti in modo prevedibile.

Etch 101: scolpire feature senza danneggiare ciò che c'è sotto

L'etch è la metà "sottrattiva" della produzione: dopo che un film è stato depositato e patternato con resist, l'etch rimuove il materiale esposto per trasferire quel pattern nello strato sottostante. Il trucco è che raramente vuoi rimuovere tutto—vuoi rimuovere un materiale specifico velocemente mentre ti fermi su un altro. Questa proprietà si chiama selettività, ed è centrale per cui le fab all'avanguardia investono così tanto nella conoscenza dei processi di etch (e perché venditori come Lam Research la perfezionano per anni).

Perché la selettività conta

Uno stack moderno può includere silicio, ossido di silicio, nitruro di silicio, metalli e hardmask. Durante l'etch, potrebbe essere necessario pulire un layer lasciando intatto lo strato di stop. Una scarsa selettività può assottigliare strati critici, spostare le dimensioni del transistor o creare percorsi di perdita che danneggiano la resa.

Etch al plasma, concettualmente

La maggior parte degli etch avanzati usa un plasma: un gas a bassa pressione energizzato in specie reattive.

Accadono due cose insieme:

- Chimica: radicali reattivi formano prodotti volatili con il materiale target (che possono essere evacuati).

- Direzionalità: campi elettrici accelerano ioni verso il wafer, dando una componente "verticale" che aiuta a scavare trincee strette e fori di contatto.

Bilanciare questi aspetti è l'arte: troppa chimica sottoincide le feature; troppa energia ionica danneggia ciò che si vuole conservare.

Come dovrebbe essere un buon etch

I team di processo cercano solitamente alcuni risultati:

- Pareti laterali verticali (così le feature corrispondono alla forma prevista)

- Danno minimo (poca rugosità superficiale, cariche intrappolate ridotte, meno disordine cristallino)

- Profili ripetibili wafer‑to‑wafer e tool‑to‑tool (affinché i passaggi a valle si comportino prevedibilmente)

Sfide comuni dell'etch

Anche con la ricetta "giusta", i wafer possono creare problemi:

- Microloading: regioni dense e sparse etchano a velocità diverse.

- Footing/notching: distorsione del profilo vicino a un'interfaccia o strato di stop.

- Rugosità: texture della parete laterale che può aumentare la resistenza o la variabilità.

- Residui: polimeri o materiale redepositato che interferiscono con depositi successivi o pulizie.

Ai nodi all'avanguardia, gestire questi dettagli spesso separa una demo di laboratorio da una produzione ad alto volume.

Patterning al limite: perché i cicli etch/deposit si moltiplicano

Quando si pensa alla scalabilità dei chip, spesso si immagina una singola macchina rivoluzionaria che stampa linee sempre più sottili. In pratica, il trasferimento del pattern è vincolato dall'intera catena—resist, hardmask, selettività di etch, stress dei film e pulizia—non da un unico strumento magico.

Hardmask stack: un pattern ha bisogno di un traduttore

Il photoresist è ottimo per catturare un pattern, ma di solito è troppo sottile e fragile per sopravvivere agli etch profondi e precisi richiesti nei dispositivi moderni. Quindi le fab costruiscono hardmask stack—film scelti con cura depositati sopra lo strato target.

Un flusso semplificato:

- Deposita uno o più layer di hardmask (spesso materiali diversi per la selettività).

- Etch il pattern di resist nell'hardmask.

- Etch l'hardmask nello strato sottostante.

- Strip/clean, poi ripeti se necessario.

Ogni film depositato è scelto non solo per la sua identità chimica, ma per come si comporterà al prossimo etch: quanto velocemente si elimina rispetto agli strati vicini, quanta rugosità genera e quanto bene mantiene la forma.

Multi‑patterning: una feature diventa molti passaggi

Quando le dimensioni critiche scendono oltre ciò che una singola passata litografica può definire, le fab usano la multi‑patterning—splitting di un pattern in più esposizioni e trasferimenti. Questo non aggiunge soltanto passi litografici; moltiplica i loop di deposizione/etch a supporto per spacer, mandrel, trim e cut mask.

Il punto è: il "pattern" su un chip all'avanguardia può essere il risultato di più cicli di depositare film e inciderli indietro con controllo rigoroso.

Perché la taratura end‑to‑end è importante

Poiché ogni passaggio cambia le condizioni iniziali per il successivo, i migliori risultati derivano dalla messa a punto della sequenza completa—materiali, condizioni di plasma, pulizia della camera e pulizie—come un unico sistema. Un piccolo miglioramento in un etch può essere azzerato (o amplificato) dalla deposizione successiva, ed è per questo che la conoscenza di integrazione processo diventa un differenziatore nel tempo.

I transistor 3D e gli alti rapporti d'aspetto aumentano la difficoltà

Rendi più semplici le revisioni dei difetti

Prepara un flusso di revisione di ispezione e difetti che il tuo team può usare lo stesso giorno.

I transistor planari erano per lo più "piatti", il che rendeva molti passaggi simili a verniciare e rifinire una superficie. La scalabilità ha spinto l'industria nel 3D: prima FinFET (una "pinna" verticale avvolta dal gate), e ora concetti gate‑all‑around (GAA) dove il gate circonda completamente il canale (spesso come nanosheet impilati).

Perché il 3D cambia la deposizione

Quando le feature hanno pareti laterali, angoli e cavità profonde, la deposizione smette di essere un semplice "coprire la sommità". I film devono essere conformi—quasi dello stesso spessore in fondo a una trincea come in superficie.

Ecco perché tecniche come ALD e CVD finemente tarate contano di più all'avanguardia: pochi atomi in meno su una parete laterale possono tradursi in resistenza maggiore, minore affidabilità o una barriera debole che permette diffusioni indesiderate.

Perché il 3D rende l'etch più esigente

L'etch deve formare il giusto profilo: pareti dritte, fondi puliti, rugosità minima e rimozione selettiva di un materiale senza consumare quello sottostante. In pattern 3D densi, anche piccoli "over‑etch" possono danneggiare regioni critiche, mentre "under‑etch" lascia residui che bloccano depositi successivi.

Molte strutture moderne hanno alto rapporto d'aspetto—molto profonde rispetto alla larghezza. Ottenere risultati uniformi su miliardi di queste feature è difficile perché reagenti, ioni e prodotti non si muovono in modo uniforme dentro e fuori spazi stretti. Problemi come microloading e danni alle pareti laterali diventano più probabili.

Nuovi materiali significano nuove superfici

GAA e interconnessioni avanzate introducono stack materiali più complessi e interfacce ultrasottili. Questo aumenta il livello di controllo per la preparazione della superficie: pre‑clean, trattamenti plasma delicati e controllo delle interfacce prima del passo di deposizione successivo. Quando la "superficie" è di poche layer atomiche, la conoscenza del processo fa la differenza tra un dispositivo funzionante e uno che fallisce silenziosamente dopo.

Resa, difetti e variabilità: dove la conoscenza di processo ripaga

La "resa" è semplicemente la percentuale di chip su un wafer che funzionano come previsto. Se un wafer contiene migliaia di chip, una piccola variazione nel tasso di difetti può tradursi in centinaia di pezzi vendibili in più. Ecco perché i produttori ossessionano numeri che sembrano piccoli—perché su scala diventano output reali.

Come i difetti diventano problemi elettrici

Molte perdite di resa non sono evidenti al microscopio; emergono come guasti elettrici. Alcuni esempi comuni:

- Opens: una linea è assottigliata o interrotta, quindi la corrente non scorre.

- Shorts: due feature che dovrebbero essere separate si toccano, creando una connessione involontaria.

- Leakage: strati isolanti troppo sottili, porosi o danneggiati lasciano passare corrente.

Deposizione ed etch possono influenzare tutti questi casi. Un film leggermente fuori spessore, composizione o uniformità può ancora "apparire ok", ma spostare il comportamento del transistor oltre i target di velocità o potenza.

Variabilità: il killer silenzioso della resa

Anche in assenza di difetti evidenti, la variazione sul wafer (o da wafer a wafer) genera chip che si comportano in modo incoerente. Un angolo è più caldo, un altro più lento, e cambia il binning del prodotto—o il pezzo fallisce. Un controllo stringente di tassi di deposizione, condizioni di plasma e selettività di etch riduce queste oscillazioni.

Metrologia e ispezione come volante

Le fab moderne non tarano i processi per intuizione. Si basano su metrologia (misura di spessori, dimensioni critiche, forma del profilo, uniformità) e ispezione (trovare particelle, difetti di pattern, problemi di bordo). I risultati alimentano aggiustamenti di processo:

- Se i profili derivano, si modifica la chimica o i tempi dell'etch.

- Se i film variano in spessore, si correggono i parametri di deposizione.

- Se i segnali di difetto aumentano, gli ingegneri risalgono alla sorgente in un modulo, condizione di camera o lotto di materiale.

In pratica questo crea anche un problema software: unire dati da strumenti, metrologia e ispezione in qualcosa su cui gli ingegneri possano agire rapidamente. I team spesso costruiscono dashboard interne, sistemi di allerta e strumenti "what changed?" per accorciare il ciclo dal segnale alla correzione. Piattaforme come Koder.ai possono aiutare qui permettendo ai team di processo e dati di generare app web leggere dalla chat—utile per integrare KPI di resa, note di escursione e storici di run senza aspettare un lungo ciclo di sviluppo tradizionale.

L'apprendimento si compone tra i nodi

La conoscenza più preziosa è incrementale: ogni nodo insegna quali difetti causano problemi, quali impostazioni derivano col tempo e quali combinazioni sono stabili. Quelle lezioni si trasportano avanti—quindi il nodo successivo parte con un playbook migliore, non con un foglio bianco.

Ricette, ripetibilità e il lungo gioco dello sviluppo di processo

Lancia un portale per il team

Metti il tuo portale interno su un dominio personalizzato così i team lo trovano facilmente.

Uno strumento di deposizione o etch non funziona con una singola "impostazione". Funziona su una ricetta—una sequenza strutturata di passaggi che definisce come il processo avviene nel tempo. Una ricetta può includere più fasi (stabilizzazione, pre‑clean, passo principale, post‑trattamento), ognuna con flussi di gas, pressione, temperatura, potenza RF, tempi e logiche di endpoint. Include anche i dettagli "silenziosi": tempi di purge, comportamento di movimentazione wafer e come la camera viene preparata prima del primo wafer.

Perché le ricette continuano a cambiare

Con il passaggio a nuovi nodi, le fab introducono nuovi materiali e nuove forme 3D—spesso contemporaneamente. Un film che funzionava su una superficie piatta può comportarsi diversamente in feature profonde e strette. Un etch che era sufficientemente selettivo nella generazione precedente può iniziare a danneggiare un liner o una barriera introdotta di recente.

Per questo le ricette evolvono: gli obiettivi di dispositivo cambiano (velocità, potenza, affidabilità), la geometria si stringe e i vincoli di integrazione si moltiplicano. Lo sviluppo di processo diventa un ciclo continuo di taratura, misurazione e ritaratura—talvolta per risolvere problemi che appaiono solo dopo migliaia di wafer.

Ripetibilità, matching e mantenersi puliti

Nella produzione ad alto volume non basta che una camera produca ottimi risultati una volta. La ripetibilità significa che la stessa ricetta dà lo stesso risultato wafer dopo wafer. Il matching tool‑to‑tool significa che una ricetta trasferita su un altro strumento (o un'altra fab) ottiene ancora spessore, profilo e uniformità entro limiti stretti—altrimenti la pianificazione e la resa soffrono.

Il controllo della contaminazione fa parte di questa realtà. Le camere "invecchiano" man mano che film si accumulano sulle superfici interne, influenzando le condizioni di plasma e il rischio particellare. Le fab dipendono da conditioning della camera, run di seasoning, pulizie e programmi di manutenzione preventiva affinché il processo resti stabile nel tempo. Quell'esperienza operativa—come mantenere le ricette performanti per mesi, non per minuti—è dove l'esperienza si accumula.

Perché costruttori di strumenti e fab co‑ottimizzano, non operano in isolamento

I chip all'avanguardia non si producono semplicemente comprando uno strumento, installandolo e premendo "run". I passaggi di deposizione e etch sono strettamente legati al layout del chip, allo stack dei materiali e agli obiettivi di affidabilità, quindi chi costruisce l'equipment e chi gestisce la fab finiscono per iterare insieme.

Il passaggio è un loop, non una linea

I progettisti di chip definiscono le strutture necessarie (per esempio contatti più piccoli, via più alti, nuovi stack di metallo). I team di integrazione di processo in fab traducono quel design in un flusso passo‑passo: deposita questo strato, patternalo, etchalo, puliscilo, ripeti. I costruttori di strumenti come Lam Research aiutano a trasformare quei requisiti in ricette producibili su hardware reale.

Quel passaggio diventa presto un loop: i primi run rivelano problemi (drift del profilo, residui, roughness dei bordi, danni imprevisti) e il feedback ritorna sia al flow di processo sia alle impostazioni dello strumento—a volte fino a opzioni hardware come materiali delle camere, sorgenti di plasma o sistemi di distribuzione gas.

Co‑ottimizzazione tra materiali, hardware e flusso

All'avanguardia non si può ottimizzare deposizione o etch in isolamento perché ogni passo cambia la condizione iniziale per il successivo. Un piccolo spostamento nella densità di film può alterare la velocità di etch; un etch più aggressivo può rendere meno conformale la deposizione successiva. La co‑ottimizzazione allinea:

- Scelte materiali (nuovi dielettrici, hardmask, layer barriera)

- Capacità dello strumento (chimica del plasma, controllo della temperatura, movimentazione wafer)

- Sequenza di processo (cicli multipli di etch/deposizione, pulizie, punti di metrologia)

I trade‑off sono reali—e gestiti deliberatamente

Le fab bilanciano costantemente throughput vs. precisione: processi più veloci possono aumentare la variabilità, mentre un controllo ultra‑stretto può ridurre i wafer/ora. Analogamente, selettività vs. danno è una tensione ricorrente: un etch molto selettivo può richiedere condizioni più rigide che rischiano rugosità o difettosità.

Il supporto di integrazione è parte del prodotto

Una parte chiave del valore fornito è il supporto di integrazione continuo—troubleshooting on‑site, matching delle performance tra camere, riduzione delle escursioni e aiuto per recuperare rapidamente quando le rese si muovono. Per la produzione ad alto volume, questa partnership conta tanto quanto le specifiche dello strumento.

Come la conoscenza produttiva si accumula tra le generazioni

"Comporre" nella produzione di chip non significa solo comprare strumenti migliori. È il modo in cui piccoli vantaggi pratici si accumulano quando i team eseguono ripetutamente le stesse classi di processi—deposizione ed etch—su più generazioni tecnologiche.

Cosa significa davvero "comporre"

In questo contesto, comporre è la ruota che gira di:

- Dati: tracce dettagliate da migliaia di wafer—drift, firme di guasto, tendenze di spessore, profili di etch.

- Esperienza: tecnici e ingegneri che imparano cosa realmente stabilizza un passo alle 2 del mattino, non solo cosa dice il manuale.

- Sequenze provate: ricette e schemi di integrazione che si sa raggiungere obiettivi proteggendo i passaggi a valle.

Niente di tutto ciò garantisce il successo, ma tipicamente accorcia il tempo dal "funziona in demo" al "funziona ogni giorno in produzione".

Loop di apprendimento: ogni ramp insegna al ramp successivo

Quando una fab rampa un nuovo nodo, affronta sfide prevedibili: variabilità, difetti, casi limite e matching tool‑to‑tool. Ogni problema risolto crea conoscenza riutilizzabile—come regolare le condizioni di plasma senza danneggiare layer sensibili, quali pulizie di camera prevengono spike di particelle o come rilevare il drift prima che diventi perdita di resa.

Col tempo questi loop rendono i ramp successivi più scorrevoli. I team partono più vicini alla destinazione perché hanno già mappato molte vie senza uscita.

I costi di switching rendono la conoscenza "collante"

Anche se un approccio alternativo sembra simile sulla carta, cambiare può essere costoso e rischioso:

- R‑qualificare processi attraverso prodotti e test di affidabilità

- Retrainare ingegneri e operatori su nuovi controlli, ganci metrologici e modalità di guasto

- Ricostruire la resa dopo che sorgenti sottili di difetto o differenze di profilo emergono

Per questo la conoscenza produttiva tende a persistere e crescere: una volta che un flow è stabile, l'incentivo è affinarlo—non ricominciare—se non ci sono benefici chiari che giustifichino il nuovo apprendimento.

Dalla capacità dello strumento all'output della fab: affidabilità e uptime contano

Pianifica prima di costruire

Mappa il tuo prossimo strumento interno prima di scrivere codice con Koder.ai Planning Mode.

Uno strumento di deposizione o etch può sembrare straordinario su una scheda tecnica—finché non deve girare 24/7 su migliaia di wafer con gli stessi risultati. Nella produzione ad alto volume, affidabilità e uptime non sono opzionali. Determinano direttamente quanti wafer buoni una fab può spedire.

Il controllo stretto è l'obiettivo

Deposizione ed etch vivono e muoiono con la stabilità del processo. Un piccolo drift in flussi gas, pressione di camera, potenza del plasma o temperatura può spostare spessore, angoli delle pareti laterali o livelli di danno—trasformando una ricetta funzionante in perdita di resa.

Per questo gli strumenti leader (inclusi i sistemi Lam Research) investono molto in hardware ripetibile: consegna RF stabile, controllo preciso dei flussi, gestione termica e sensori che catturano le escursioni precocemente.

L'output dipende dalla manutenzione tanto quanto dalla fisica

Anche con un processo perfetto, la produzione soffre quando gli strumenti sono spesso fermi. L'output reale di una fab è modellato da:

- Manutenzione pianificata (pulizie, seasoning delle camere, sostituzioni kit)

- Fermi non pianificati (eventi particellari, instabilità di plasma, problemi alle pompe)

- Logistica dei pezzi (avere i consumabili giusti in sito, non bloccati in transito)

Uno strumento più facile da manutenere—supportato da un buon forecasting dei ricambi—mantiene più camere operative e più lotti in movimento.

L'affidabilità diventa costo e programma

Un uptime maggiore tipicamente riduce il costo per wafer: meno operatori inattivi, migliore utilizzo dello spazio pulito costoso e meno tempo perso in rilavorazioni. Ugualmente importante, la disponibilità coerente rende prevedibili i programmi di consegna, fondamentale quando i passi a valle sono strettamente in coda.

Una realtà in più: passare da demo di laboratorio a produzione di massa stressa gli strumenti in modo diverso. Run prolungati, maggior numero di wafer e budget di difetti più stringenti espongono rapidamente i punti deboli—quindi l'ingegneria dell'affidabilità diventa parte integrante della "capability di processo".

Cosa tenere d'occhio: pressione di scaling e prossimi colli di bottiglia di processo

Man mano che i chip spingono verso nodi più piccoli e strutture 3D, il progresso dipende sempre più dalla ripetizione di cicli di deposizione ed etch con precisione estrema—spesso centinaia di volte in un singolo stack di dispositivo. Il "prossimo collo di bottiglia" raramente è una singola svolta, ma la difficoltà cumulativa di mantenere ogni ciclo consistente preservando resa, controllando la variabilità e rampando processi nuovi abbastanza in fretta per soddisfare la domanda.

Dove si concentra la pressione

Alcune tendenze che metteranno più sotto stress deposizione/etch:

- Nuove architetture di dispositivo (GAA/nanosheet, CFET): spazi più stretti e strati più sottili aumentano la sensibilità a piccoli errori di spessore o profondità di etch.

- Backside power delivery: aggiunge nuove superfici, nuovi passi di integrazione e nuovi modi di guasto che vanno gestiti senza danneggiare il front‑side.

- Processi selettivi: maggiore dipendenza da "deposita qui, non lì" e "etcha questo, non quello", alzando l'asticella per selettività e controllo dei difetti.

- Complessità dei materiali: film, liner e barriere più esotici che devono essere uniformi, a basso difetto e compatibili con i passaggi a valle.

- Aspettative sulla velocità di ramp: le transizioni di nodo si giudicano non solo per la capacità, ma per la rapidità con cui la resa si stabilizza a volume.

Lista di controllo rapida per lettori non tecnici

Quando confronti fornitori di strumenti o approcci di fab (inclusi Lam Research e pari grado), concentrati sui risultati:

- Miglioramento della resa: il processo riduce i difetti killer a scala?

- Controllo della variabilità: quanto stretti sono i risultati within‑wafer e wafer‑to‑wafer?

- Velocità di ramp: quanto rapidamente un nuovo nodo raggiunge produzione stabile ad alto volume?

- Ripetibilità e uptime: gli strumenti restano coerenti su run lunghi con downtime minimo?

Per approfondire, consulta gli explainers correlati su /blog. Se stai valutando opzioni—o costruendo strumenti interni per analizzare resa, escursioni e metriche di ramp—consulta /pricing per come consideriamo costo, velocità e capacità (incluso quando una piattaforma build‑with‑chat come Koder.ai può sostituire una pipeline software legacy più lenta).