Waarom depositie en etsen centraal staan bij schaalverkleining van chips

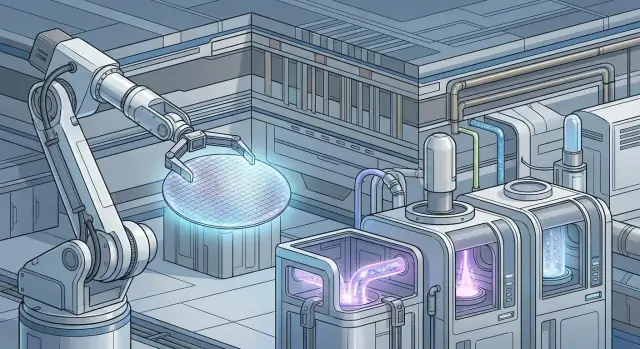

Als je chipfabricage terugbrengt tot de meest herhaalbare bewegingen, verschijnen twee acties keer op keer: depositie en etsen.

Depositie is de "toevoeg"-stap. Apparatuur brengt ultradunne films aan—geleiders, isolatoren of speciale barrièrelagen—op een wafer, soms maar een paar atomen per keer. Etsen is de "verwijder"-stap. Apparatuur snijdt selectief materiaal weg om de piepkleine structuren te vormen die transistors en bedrading worden, bij voorkeur zonder de onderliggende lagen te beschadigen.

Naarmate chips kleiner zijn geworden, zijn deze twee stappen de belangrijkste knoppen geworden die ingenieurs gebruiken om te sturen wat op nanometerschaal het meest telt: dikte, vorm en interfaces. Daarom zitten apparatuurbedrijven zoals Lam Research dicht bij het hart van toonaangevende productie.

Wat “leading-edge” eigenlijk betekent

“Leading-edge” verwijst doorgaans naar de meest geavanceerde, grootschalige productienodes—waar dichtheid, vermogen en prestaties het meest ambitieus zijn en de foutmarge het kleinst. Het gaat niet alleen om een marketinggetal; hier verschijnen nieuwe apparaatstructuren en nieuwe materialen het eerst.

Het cumulerende voordeel

Tool-capaciteit doet ertoe (uniformiteit, selectiviteit, schadebeheersing, throughput). Maar proceskennis is net zo belangrijk: de recepten, integratietrucs, metrologieterugkoppeling en defectinzichten die van een prima tool een stabiel, hoog-opbrengst fabproces maken.

Dat voordeel stapelt zich op over technologiegeneraties omdat elke nieuwe node niet bij nul begint—ze bouwt voort op eerdere lessen over hoe films groeien, hoe plasma's zich gedragen en hoe kleine variaties grote verschuivingen in opbrengst kunnen veroorzaken.

Wat we hierna behandelen

Om te zien waarom depositie- en etscycli zich blijven vermenigvuldigen, kijken we naar:

- Patterning aan de grens en waarom herhaalde "deposit–etch–clean"-lussen gebruikelijk zijn

- 3D-structuren (features met hoge aspect ratio) die moeilijker te vullen en te etsen zijn

- Opbrengstleren, defecten en variabiliteit—waar ervaring loont

- Terugkoppelingslussen tussen toolmakers en fabs die verbetering versnellen

Van lagen naar logica: hoe moderne chips daadwerkelijk worden opgebouwd

Een moderne chip wordt niet "gefreesd" uit een blok silicium. Hij wordt opgebouwd—meer als een microscopische laagjestort—door herhaaldelijk ultradunne films aan te brengen, ze te patternen en selectief te verwijderen wat je niet wilt. Doe dat honderden keren en je eindigt met transistors, bedrading en isolerende barrières gestapeld en verweven in 3D.

De herhalende lus: toevoegen, patternen, verwijderen

Op hoog niveau doorloopt chipfabricage een bekend ritme:

- Depositie legt een film neer (metaal, oxide, nitride en meer), vaak maar een paar atomen tot enkele nanometers dik.

- Patterning bepaalt waar die film moet blijven (met lithografie om een masker te maken).

- Etsen verwijdert blootgestelde gebieden en draagt het patroon over in de film.

Elke lus creëert een "slice" van het uiteindelijke apparaat—gate-structuren, contactgaten of interconnectlijnen—totdat de logica en het geheugen van de chip uit de stapel verschijnen.

Waarom piepkleine features extreme controle vragen

Als features worden gemeten in enkele nanometers, is controle over dikte en vorm geen luxe meer. Een film die iets te dik is, kan een smalle opening dichtknijpen; een etsstap die iets te agressief is, kan een lijn verbreden of een onderliggende laag raken. Zelfs kleine profielveranderingen—hoek van de zijwand, afronding van hoeken, oppervlakte-ruwheid—kunnen de stroomvoering beïnvloeden.

Processtappen, procesvensters en opbrengst

Productie is georganiseerd in processtappen (specifieke depositie/ets-bewerkingen) die binnen een procesvenster moeten draaien—het bereik van instellingen waaruit de resultaten consequent acceptabel zijn. Naarmate chips dichter worden, krimpen die vensters. En omdat latere lagen op eerdere bouwen, kan een kleine afwijking zich opstapelen tot uitlijningsoffsets, shorts, opens en uiteindelijk lagere opbrengst.

Depositie 101: films aanbrengen met atomaire precisie

Depositie is de "materiaal toevoegen"-helft van chipfabricage: het bouwen van ultradunne films op een wafer zodat latere stappen kunnen patternen, beschermen of elektrisch isoleren wat eronder zit. Deze films zijn niet decoratief—elke laag is gekozen voor een specifieke rol en moet betrouwbaar werken over miljarden kleine features.

De drie belangrijkste benaderingen: CVD, PVD en ALD

Chemical Vapor Deposition (CVD) gebruikt reactieve gassen die een vaste film vormen op het waferoppervlak. Het wordt veel gebruikt voor vele dielectrica en sommige geleidende lagen omdat het grote gebieden efficiënt en met goede uniformiteit kan bedekken.

Physical Vapor Deposition (PVD) (vaak "sputteren") slaat atomen van een doelmateriaal los en deponeert ze op de wafer. PVD is gebruikelijk voor metalen en hardmask-materialen, vooral wanneer je een dichte film wilt—maar het kan moeite hebben om zijwanden van zeer diepe, smalle structuren te coaten.

Atomic Layer Deposition (ALD) depositeert materiaal één moleculaire "dosis" per keer via zelfbegrenzende oppervlakreacties. Het is trager, maar excelleert wanneer controle en dekking belangrijker zijn dan snelheid—vooral in de meest krappe 3D-features.

Toen chips naar vinnen, greppels en verticale gaten gingen, werd depositie geen eenvoudig "toplaagje"-probleem meer. Conformiteit beschrijft hoe gelijkmatig een film de bovenkant, zijwanden en bodem van een feature bedekt.

Als een laag dun is op de zijwand of de opening dichtknijpt, kun je elektrische lekken, slechte vulling of falen in latere etsstappen krijgen. Hoge conformiteit is cruciaal voor diepe, smalle features waar weinig speling is.

Filmeigenschappen die opbrengst kunnen maken of breken

Zelfs als de dikte correct is, moet de film aan meerdere praktische eisen voldoen:

- Uniformiteit: consistente dikte over de hele wafer en van wafer tot wafer.

- Vervuilingen: ongewenste atomen kunnen elektrisch gedrag veranderen of betrouwbaarheidsproblemen veroorzaken.

- Spanning: films die te trekkend of samendrukkend zijn kunnen structuren vervormen of scheuren.

- Hechting: lagen moeten hechten tijdens thermische cycli, reiniging en etsen.

Intuïtieve voorbeelden: wat deze lagen echt doen

- Liners coaten zijwanden van features om oppervlakken te beschermen en de startcondities voor latere vullingen te bepalen.

- Barrières houden metalen tegen om in omliggende materialen te diffunderen (kritisch voor betrouwbaarheid).

- Hardmasks fungeren als stevige sjablonen die agressieve etsen beter doorstaan dan photoresist.

- Dielectricalagen isoleren elektrisch en scheiden geleiders—essentieel om shorts te voorkomen.

Aan het toonaangevende einde is depositie niet zomaar "een film toevoegen." Het is precies materiaalontwerp, afgestemd zodat elke volgende etsstap en patterning voorspelbaar werkt.

Etsen 101: features uitsnijden zonder te beschadigen wat eronder zit

Etsen is de "substractieve" helft van chipfabricage: nadat een film is gedeponeerd en gepatenteerd met resist, verwijdert etsen het blootgestelde materiaal om dat patroon in de onderliggende laag over te dragen. De truc is dat je zelden alles wilt weghalen—je wilt één specifiek materiaal snel verwijderen terwijl je op een ander stopt. Dat noemen we selectiviteit, en het is essentieel waarom toonaangevende fabs zoveel investeren in etstechnologie en waarom toolleveranciers zoals Lam Research er jaren aan werken.

Waarom selectiviteit ertoe doet

Een moderne stack kan silicium, siliciumoxide, siliciumnitride, metalen en hardmasks bevatten. Tijdens etsen wil je soms één laag volledig vrijmaken terwijl een "etch stop" intact blijft. Slechte selectiviteit kan kritische lagen dunner maken, transistorafmetingen verschuiven of lekpaden creëren die opbrengst schaden.

Plasma-ets, conceptueel

De meeste geavanceerde etsen gebruiken een plasma: een laagdrukgas dat wordt omgezet in reactieve deeltjes.

Tegelijkertijd gebeurt er twee dingen:

- Chemie: reactieve radicalen vormen vluchtige bijproducten met het doelmateriaal (zodat ze kunnen worden weggepompt).

- Directionalisatie: elektrische velden versnellen ionen richting de wafer, wat een "recht-omlaag" component geeft die helpt smalle greppels en contactgaten te snijden.

Het vinden van de balans is kunst: te veel chemie kan features onderuithalen; te veel ionenergie kan beschadigen wat je juist wilt behouden.

Hoe een goede etsstap eruitziet

Procesgroepen jagen meestal op een paar uitkomsten:

- Verticale zijwanden (zodat features de bedoelde vorm krijgen)

- Minimale schade (weinig oppervlakte-ruwheid, minder vastzittende ladingen, minder kristalverstoring)

- Herhaalbare profielen van wafer tot wafer en tool tot tool (zodat downstream-stappen voorspelbaar blijven)

Veelvoorkomende etsonderwerpen

Zelfs als het recept "juist" is, vechten echte wafers terug:

- Microloading: dicht en open patroongebied etsen met verschillende snelheden.

- Footing/notching: profielvervorming nabij een interface of etch-stoplaag.

- Ruwheid: zijwandtextuur die weerstand of variabiliteit kan vergroten.

- Residu's: polymeren of gerevodeerd materiaal dat latere depositie of reiniging hindert.

Bij leading nodes is het beheren van deze details vaak het verschil tussen een labdemo en grootschalige productie.

Patterning aan de limiet: waarom etsen/depositiecycli zich vermenigvuldigen

Als mensen aan schaalverkleining denken, stellen ze zich vaak één doorbraakmachine voor die steeds kleinere lijnen "print". In de praktijk wordt patroonoverdracht beperkt door de hele keten—resist, hardmasks, etch-selectiviteit, filmspanning en reiniging—niet door één magische tool.

Hardmask-stacks: een patroon heeft een vertaler nodig

Photoresist is uitstekend om een patroon vast te leggen, maar is meestal te dun en te fragiel om diepe, precieze etsen te overleven. Dus fabs bouwen hardmask-stacks—zorgvuldig gekozen films bovenop de doellaag.

Een vereenvoudigde flow ziet er zo uit:

- Depositie van één of meer hardmask-lagen (vaak verschillende materialen voor selectiviteit).

- Etsen van het resistpatroon in het hardmask.

- Etsen van het hardmask-patroon in de onderliggende film.

- Strip/clean, en herhaal indien nodig.

Elke gedeponeerde film wordt gekozen op basis van hoe hij zich gedraagt tijdens de volgende etsstap: hoe snel hij etst ten opzichte van naburige lagen, hoeveel ruwheid hij creëert en hoe goed hij zijn vorm behoudt.

Multi-patterning: één feature wordt meerdere stappen

Wanneer kritische dimensies kleiner worden dan wat een enkele lithografiepoging betrouwbaar kan definiëren, gebruiken fabs multi-patterning—het opsplitsen van één dicht patroon in meerdere belichtingen en overbrengingen. Dat voegt niet alleen lithografiestappen toe; het vermenigvuldigt de ondersteunende depositie/ets-lussen voor spacers, mandrels, trims en cut-masks.

De clou: het "patroon" op een toonaangevende chip kan het resultaat zijn van meerdere cycli van films deponeren en terugetsen met strakke controle.

Waarom end-to-end afstemming ertoe doet

Omdat elke stap de startconditie voor de volgende verandert, komen de beste resultaten voort uit het afstemmen van de volledige reeks—materialen, plasma-condities, chamber-netheid en reinigingen—als één systeem. Een kleine verbetering in één etsstap kan door de volgende depositie worden weggevaagd (of versterkt), wat verklaart waarom procesintegratie-kennis over tijd een onderscheidende factor wordt.

3D-transistors en hoge aspect ratio’s verhogen de moeilijkheidsgraad

Plan voordat je bouwt

Plan je volgende interne tool voordat je gaat programmeren met Koder.ai Planning Mode.

Platte (planar) transistors waren grotendeels "vlak", wat veel stappen leek op het verven en bijsnijden van een oppervlak. Schaling duwde de industrie in 3D: eerst FinFETs (een verticale "fin" omwikkeld door de gate), en nu gate-all-around (GAA)-concepten waarbij de gate het kanaal volledig omsluit (vaak als gestapelde nanosheets).

Waarom 3D depositie verandert

Zodra features zijwanden, hoeken en diepe holtes hebben, is depositie geen eenvoudige "bovenkant coaten"-taak meer. Films moeten conform zijn—bijna dezelfde dikte in de bodem van een greppel als op het bovenste oppervlak.

Daarom zijn technieken als ALD en zorgvuldig afgestemde CVD-stappen belangrijker aan de leading edge: een paar atomen te dun op een zijwand kunnen hogere weerstand, slechtere betrouwbaarheid of een zwakke barrière veroorzaken waardoor materialen ongewenst diffunderen.

Waarom 3D etsen kieskeuriger maakt

Etsen moet het juiste profiel vormen: rechte wanden, schone bodems, minimale ruwheid en selectieve verwijdering van één materiaal zonder de laag eronder aan te vreten. In dichte 3D-patronen kan kleine "over-etch" kritieke regio's raken, terwijl "under-etch" residu achterlaat dat latere depositie blokkeert.

Veel moderne structuren hebben een hoge aspect ratio—zeer diep vergeleken met hoe smal ze zijn. Gelijkmatige resultaten over miljarden van deze features bereiken is moeilijk omdat reactanten, ionen en bijproducten niet gelijkmatig in- en uitstromen in krappe ruimtes. Problemen als microloading en zijwandschade worden waarschijnlijker.

Nieuwe materialen betekenen nieuwe oppervlakken

GAA en geavanceerde interconnects brengen complexere materiaalstacks en ultradunne interfaces. Dat verhoogt de eisen voor oppervlaktevoorbereiding: pre-cleans, zachte plasmabehandelingen en interfacecontrole voor de volgende depositiestap. Wanneer het "oppervlak" maar een paar atomaire lagen dik is, maakt proceskennis het verschil tussen een werkend apparaat en een dat later stilletjes faalt.

Opbrengst, defecten en variabiliteit: waar proceskennis rendeert

"Yield" is simpelweg het aandeel chips op een wafer dat werkt zoals bedoeld. Als een wafer duizenden chips bevat, kan een kleine verandering in defecttarief honderden extra verkoopbare onderdelen betekenen. Daarom zijn fabrikanten geobsedeerd door wat als kleine cijfers klinkt—want op schaal worden kleine verbeteringen écht product.

Hoe defecten elektrische problemen worden

Veel opbrengstverliezen zijn niet dramatisch onder de microscoop; ze verschijnen als elektrische fouten. Enkele voorbeelden:

- Opens: een lijn wordt dunner of onderbroken, waardoor stroom niet kan vloeien.

- Shorts: twee features die gescheiden moeten zijn, raken elkaar en vormen een ongewenste verbinding.

- Lekkage: isolatielagen worden te dun, te poreus of beschadigd, waardoor stroom kan "lekken".

Depositie- en etsstappen beïnvloeden al deze gevallen. Een film die iets afwijkt in dikte, samenstelling of uniformiteit kan er nog "oké" uitzien, maar transistorprestaties genoeg verschuiven om snelheid- of vermogendoelen te missen.

Variabiliteit: de stille opbrengstdoder

Zelfs zonder duidelijke defecten zorgt variatie over de wafer (of van wafer tot wafer) voor chips die inconsistent presteren. Een hoek loopt heter, een andere is trager, en plotseling verandert product-binning—of faalt het onderdeel. Strakke controle van depositiesnelheden, plasma-condities en etch-selectiviteit verkleint deze schommelingen.

Metrologie en inspectie als stuurwiel

Moderne fabs stemmen processen niet af op intuïtie. Ze vertrouwen op metrologie (dikte meten, kritische dimensies, profielvorm, uniformiteit) en inspectie (deeltjes, patroonfouten, randproblemen). De resultaten voeden procesaanpassingen:

- Als profielen afwijken, wordt etschemie of timing aangepast.

- Als films in dikte variëren, worden depositieparameters gecorrigeerd.

- Als defectsignaturen pieken, traceren ingenieurs de bron naar een specifiek module, chamberconditie of materiaalpartij.

In de praktijk creëert dit ook een softwareuitdaging: data van tools, metrologie en inspectie aan elkaar koppelen zodat ingenieurs snel kunnen ingrijpen. Teams bouwen vaak interne dashboards, waarschuwingen en "wat is er veranderd?"-hulpmiddelen om de cyclus van signaal naar oplossing te verkorten. Platformen zoals Koder.ai kunnen hier helpen door proces- en datateams in staat te stellen lichtgewicht webapps vanuit chat te maken—handig om yield-KPI's, afwijkingsnotities en runhistorie snel te integreren zonder te wachten op langdurige ontwikkeltrajecten.

Leren stapelt zich op over nodes

De meest waardevolle know-how is incrementeel: elke node leert welke defecten bepaalde oorzaken hebben, welke instellingen met de tijd drift vertonen en welke combinaties stabiel zijn. Die lessen draag je mee—zodat de volgende node begint met een betere handleiding, niet met een leeg vel.

Recepten, herhaalbaarheid en het lange spel van procesontwikkeling

Maak defectreviews makkelijker

Stel een inspectie- en defectreviewworkflow op die je team diezelfde dag kan gebruiken.

Een depositie- of etstoestel draait niet op één enkele "instelling." Het draait op een recept—een gestructureerde volgorde van stappen die bepaalt hoe het proces zich in de tijd afspeelt. Een recept kan meerdere fasen omvatten (stabiliseren, pre-clean, hoofdhandeling, nabehandeling), elk met eigen gasstromen, druk, temperatuur, RF-vermogen, timing en endpoint-logica. Het bevat ook de "stille" details: purgetijden, waferhandling-gedrag en hoe de kamer wordt voorbereid vóór de eerste wafer.

Waarom recepten blijven veranderen

Naarmate chips naar nieuwe nodes gaan, introduceren fabs vaak nieuwe materialen en nieuwe 3D-vormen—vaak gelijktijdig. Een film die op een vlak oppervlak werkte, kan zich anders gedragen in diepe, smalle features. Een etsstap die eerder selectief genoeg was, kan beginnen een nieuw geïntroduceerde liner of barrière te beschadigen.

Daarom evolueren recepten: apparaatdoelen veranderen (snelheid, vermogen, betrouwbaarheid), geometrie wordt strakker en integratiebeperkingen nemen toe. Procesontwikkeling wordt een langdurige cyclus van afstemmen, meten en opnieuw afstemmen—soms om problemen op te lossen die pas na duizenden wafers verschijnen.

Herhaalbaarheid, matching en schoon blijven

In massaproductie is het niet genoeg dat één chamber één keer uitstekende resultaten levert. Herhaalbaarheid betekent dat hetzelfde recept telkens hetzelfde resultaat geeft. Tool-to-tool matching betekent dat een recept dat naar een andere tool (of fabriek) wordt overgezet, nog steeds binnen strikte grenzen dezelfde dikte, profiel en uniformiteit haalt—anders lijdt productieplanning en opbrengst.

Contaminatiecontrole hoort hierbij. Chambers "verouderen" als films zich op interne oppervlakken ophopen, wat plasma-condities en deeltjesrisico beïnvloedt. Fabs vertrouwen op chamber conditioning, inloopruns, reinigingen en preventief onderhoud zodat processen stabiel blijven. Die operationele know-how—hoe je recepten maandenlang laat presteren, niet slechts minuten—is waar ervaring zich opstapelt.

Toonaangevende chips worden niet gemaakt door simpelweg een tool te kopen, te installeren en op "run" te drukken. Depositie- en etsstappen zijn nauw verbonden met het layout van de chip, de materiaalstack en betrouwbaarheidseisen, dus mensen die de apparatuur bouwen en mensen die de fab runnen, itereren vaak samen.

De overdracht is een lus, geen lijn

Chipontwerpers definiëren structuren die ze nodig hebben (bijv. kleinere contacten, hogere vias, nieuwe metalen stacks). Procesintegratieteams in de fab vertalen dat ontwerp naar een stap-voor-stap flow: deponeer deze laag, pattern, etsen, reinigen, herhaal. Toolmakers zoals Lam Research helpen vervolgens die eisen om te zetten naar produceerbare recepten op echte hardware.

Die overdracht wordt snel een lus: vroege runs tonen issues (profieldrift, residu, line-edge ruwheid, onverwachte schade), en feedback gaat terug naar zowel procesflow als toolinstellingen—soms zelfs naar hardwarekeuzes zoals kamermaterialen, plasma-bronnen of gaslevering.

Co-optimisatie over materialen, hardware en flow

Aan de leading edge kun je depositie of etsen niet geïsoleerd optimaliseren omdat elke stap de startconditie voor de volgende verandert. Een kleine verandering in filmdichtheid kan de etssnelheid veranderen; een agressievere etsstap kan latere depositie minder conform maken. Co-optimisatie brengt op één lijn:

- Materiaalkeuzes (nieuwe dielectrica, hardmasks, barrierelagen)

- Tool-capaciteit (plasmachemie, temperatuurcontrole, waferhandling)

- Processequencing (meervoudige etz/depositie-cycli, reinigingen, metriekapunt

De afwegingen zijn reëel—en worden bewust beheerd

Fabs balanceren constant throughput vs. precisie: snellere verwerking kan variabiliteit verhogen, terwijl ultra-strakke controle het aantal wafers per uur kan verlagen. Evenzo is selectiviteit vs. schade een terugkerende spanning: een etsstap die sterk één materiaal verkiest, kan zwaardere condities vereisen die ruwheid of defectiviteit risico verhogen.

Integratie-support is onderdeel van het product

Een belangrijk deel van de geleverde waarde is voortdurende integratieondersteuning—on-site troubleshooting, performance matching tussen chambers, het verminderen van afwijkingen en snel herstel als opbrengst verandert. Voor hoogvolumeproductie kan die samenwerking net zoveel waard zijn als de specificaties op papier.

Hoe productiekennis zich opstapelt over generaties

"Cumuleren" in chipfabricage gaat niet alleen om betere tools kopen. Het is de manier waarop kleine, praktische voordelen zich opstapelen wanneer teams herhaaldelijk dezelfde klassen processen draaien—depositie en etsen—over meerdere technologiegeneraties.

Wat “cumuleren” echt betekent

In deze context is compounding het vliegwiel van:

- Data: gedetailleerde traces van duizenden wafers—drift, fouthandtekeningen, filmdikte-trends, etch-profielen.

- Ervaring: technici en ingenieurs die leren wat echt een stap stabiliseert om 2 uur 's nachts, niet alleen wat het handboek zegt.

- Bewezen sequenties: procesrecepten en integratiepatronen die bekend zijn om targets te halen en downstream-stappen te beschermen.

Niets hiervan garandeert succes, maar het verkort meestal de tijd van "werkt in een demo" naar "werkt elke dag in productie."

Leer-lussen: elke ramp leert de volgende ramp

Wanneer een fab een nieuwe node opschaalt, komt hij voorspelbare uitdagingen tegen: variabiliteit, defecten, randgevallen en tool-to-tool matching. Elk opgelost probleem creëert herbruikbare kennis—hoe plasma-condities af te stemmen zonder gevoelige lagen te beschadigen, welke kamerreinigingen deeltjespieken voorkomen of hoe drift te detecteren voordat het als opbrengstverlies zichtbaar wordt.

In de loop der tijd maken die leer-lussen latere opschaling soepeler. Teams beginnen dichter bij het doel omdat ze vele doodlopende paden al in kaart hebben gebracht.

Overschakelkosten maken know-how "plakkerig"

Zelfs als een andere aanpak op papier vergelijkbaar lijkt, kan overschakelen duur en risicovol zijn:

- Re-kwalificatie van processen over producten en betrouwbaarheidstests

- Opleiden van ingenieurs en operators op nieuwe controls, metriekintegraties en faalwijzen

- Opbouw van opbrengst na subtiele defectbronnen of profielverschillen

Daarom blijft productiekennis vaak bestaan en groeien: als een procesflow stabiel is, is de stimulans om te verfijnen groter dan om opnieuw te beginnen—tenzij de voordelen duidelijk het herleren waard zijn.

Prototypeer proces-tools snel

Prototypeer een metrologie-rapportage-UI in React met een Go- en Postgres-backend via chat.

Een depositie- of etstoestel kan op papier geweldig zijn—totdat het 24/7 duizenden wafers moet draaien met hetzelfde resultaat. In hoogvolumeproductie zijn betrouwbaarheid en uptime geen luxe. Ze bepalen rechtstreeks hoeveel goede wafers een fab kan leveren.

Strakke controle is het hele punt

Depositie en etsen leven en sterven bij processtabiliteit. Kleine drifts in gasstromen, kamerdruk, plasmavermogen of temperatuur kunnen filmdikte, zijwandhoeken of schadelevels verschuiven—waardoor een werkend recept in opbrengstverlies verandert.

Daarom investeren toonaangevende tools (inclusief Lam Research-systemen) zwaar in reproduceerbare hardware: stabiele RF-levering, precieze massflow-control, thermisch beheer en sensoren die afwijkingen vroeg signaleren.

Output hangt af van onderhoud net zozeer als van fysica

Zelfs als het proces perfect is, lijdt productie als tools vaak stilvallen. De echte fab-output wordt bepaald door:

- Gevraagde onderhoudsintervallen (reinigingen, chamber-seasoning, kit-swaps)

- Ongeplande downtime (deeltjevenementen, plasma-instabiliteit, pompissues)

- Onderdelenlogistiek (de juiste verbruiksartikelen op locatie hebben, niet vast in transport)

Een tool die gemakkelijker te onderhouden is—en ondersteund wordt door goede voorraadplanning—houdt meer chambers draaiende en meer lots in beweging.

Betrouwbaarheid wordt kosten en planning

Hogere uptime verlaagt doorgaans de kost per wafer: minder stilstand van operators, betere benutting van dure cleanroomruimte en minder tijd kwijt aan herwerk. Net zo belangrijk maakt consistente beschikbaarheid leveringsschema's voorspelbaar, wat telt als downstream-stappen strak in de wachtrij staan.

Nog een realiteit: opschalen van labdemo's naar massaproductie belast tools anders. Lange runs, hogere waferstarts en strengere defectbudgetten leggen zwakke plekken snel bloot—dus betrouwbaarheidstechniek wordt een kernonderdeel van “procescapability.”

Waar je op moet letten: opschalingsdruk en de volgende procesknelpunten

Naarmate chips kleinere nodes en meer 3D-structuren krijgen, hangt vooruitgang steeds meer af van het herhalen van depositie- en etsstappen met extreme precisie—vaak honderden keren in één apparaatsstack. De "volgende bottleneck" is meestal geen enkele doorbraak, maar de cumulatieve moeilijkheid om elke cyclus consistent te houden terwijl je opbrengst behoudt, variabiliteit controleert en processen snel genoeg opschaalt om aan de vraag te voldoen.

Waar de druk zich concentreert

Meerdere trends zullen depositie/ets het meest belasten:

- Nieuwe apparaatarchitecturen (GAA/nanosheet, CFET): nauwere ruimtes en dunnere lagen verhogen gevoeligheid voor kleine filmdikte- of etsdieptefouten.

- Backside power delivery: voegt nieuwe oppervlakken, integratiestappen en faalwijzen toe die moeten worden beheerd zonder de voorzijde te schaden.

- Selectieve processen: meer afhankelijkheid van "deponeren hier, niet daar" en "etsen dit, niet dat", waardoor de lat voor selectiviteit en defectcontrole hoger komt te liggen.

- Materiaalkomplexiteit: exotischere films, liners en barrierelagen die uniform, laag-defect en compatibel met downstream-stappen moeten zijn.

- Snelheid van opschaling: node-overgangen worden beoordeeld op niet alleen capaciteit, maar ook hoe snel opbrengst op volume stabiliseert.

Een korte checklist voor niet-technische lezers

Bij het vergelijken van toolvendors of fab-aanpakken (inclusief Lam Research en concurrenten), richt je op uitkomsten:

- Opbrengstverbetering: reduceert het proces kritieke defects op schaal?

- Variabiliteitscontrole: hoe strak zijn binnen-wafer en wafer-tot-wafer resultaten?

- Opschalingssnelheid: hoe snel bereikt een nieuwe node stabiele, grootschalige productie?

- Herhaalbaarheid en uptime: blijven tools consistent tijdens lange runs met minimale stilstand?

Als je dieper wilt graven, bekijk gerelateerde explainers op /blog. Als je opties evalueert—or interne tooling bouwt om opbrengst, afwijkingen en ramp-metrics te analyseren—zie /pricing voor hoe wij denken over kosten, snelheid en capaciteit (inclusief wanneer een build-with-chat platform zoals Koder.ai een trager, legacy softwaretraject kan vervangen).