04 พ.ค. 2568·3 นาที

Lam Research และข้อได้เปรียบการทบเพิ่มในการผลิตชิป

เครื่องมือฝากชั้นและการกัดมีบทบาทสำคัญในชิปขั้นนำ ทำไมความรู้กระบวนการจึงทบเพิ่มข้ามโหนด และผลกระทบต่อผลผลิต การสเกล และการเร่งการขยับโหนด

เครื่องมือฝากชั้นและการกัดมีบทบาทสำคัญในชิปขั้นนำ ทำไมความรู้กระบวนการจึงทบเพิ่มข้ามโหนด และผลกระทบต่อผลผลิต การสเกล และการเร่งการขยับโหนด

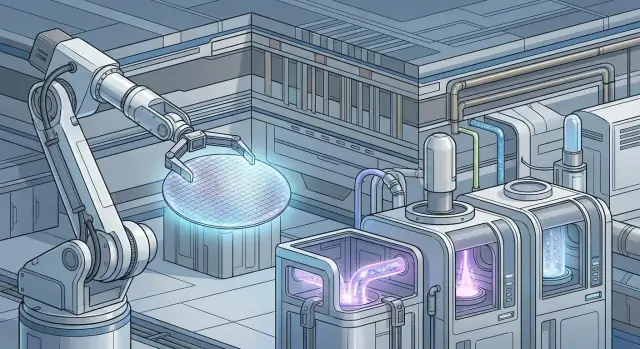

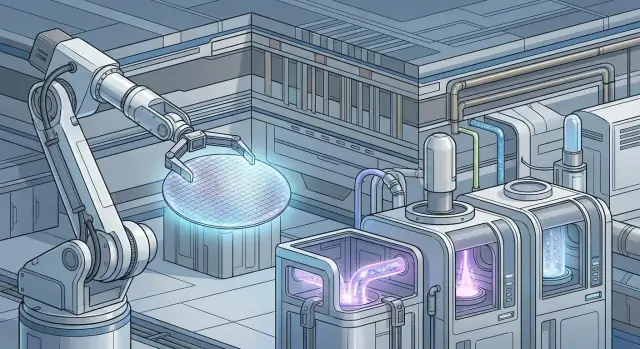

ถ้าคุณลดการผลิตชิปลงเหลือการเคลื่อนไหวที่ทำซ้ำได้มากที่สุด สองการกระทำจะปรากฏขึ้นซ้ำแล้วซ้ำอีก: การฝากชั้น (deposition) และ การกัด (etch).

Deposition คือขั้นตอน “เพิ่ม” เครื่องมือจะวางฟิล์มบางมาก—เป็นตัวนำ ชั้นฉนวน หรือชั้นกั้นพิเศษ—บนเวเฟอร์ บางครั้งทีละไม่กี่อะตอม Etch คือขั้นตอน “ลบ” เครื่องมือจะเจาะวัสดุออกอย่างคัดเลือกเพื่อสร้างฟีเจอร์จิ๋วที่กลายเป็นทรานซิสเตอร์และเส้นสื่อไฟฟ้า โดยหวังว่าจะไม่ทำร้ายชั้นด้านล่าง

เมื่อชิปถูกสเกลลง สองขั้นตอนนี้กลายเป็นปุ่มหลักที่วิศวกรใช้ควบคุมสิ่งที่สำคัญที่สุดในมิติระดับนาโน: ความหนา รูปร่าง และอินเตอร์เฟซ นั่นคือเหตุผลที่บริษัทอุปกรณ์อย่าง Lam Research อยู่ใกล้หัวใจของการผลิตชั้นนำ

“Leading-edge” โดยทั่วไปหมายถึงโหนดการผลิตที่ก้าวหน้าที่สุดในปริมาณการผลิตสูง—ที่ซึ่งความหนาแน่น กำลัง และประสิทธิภาพมีความต้องการเข้มงวด และช่องว่างต่อความผิดพลาดแคบมาก มันไม่ใช่แค่ตัวเลขการตลาด แต่คือที่ที่โครงสร้างอุปกรณ์และวัสดุใหม่ปรากฏตัวก่อน

ความสามารถของเครื่องมือมีความสำคัญ (ความสม่ำเสมอ, ความเลือกทางวัสดุ, การควบคุมความเสียหาย, อัตราผลผลิต) แต่ ความรู้ด้านกระบวนการมีความสำคัญไม่แพ้กัน: สูตรการทำงาน เทคนิคการผสาน ผลตอบรับจากเมโทรโลยี และการเรียนรู้จากข้อบกพร่อง ที่เปลี่ยนเครื่องมือดีให้เป็นกระบวนการโรงงานที่เสถียรและมีผลผลิตสูง

ข้อได้เปรียบนี้ทบเพิ่มข้ามเจเนอเรชันของเทคโนโลยีเพราะทุกโหนดใหม่ไม่ได้เริ่มจากศูนย์—มันสร้างจากการเรียนรู้ก่อนหน้าเกี่ยวกับการเติบโตของฟิล์ม พฤติกรรมของพลาสมา และการเปลี่ยนแปลงเล็ก ๆ ที่สามารถทำให้ผลผลิตผันผวนอย่างมาก

เพื่อเห็นว่าทำไมรอบการฝากและกัดจึงเพิ่มขึ้น เราจะมองไปที่:

ชิปสมัยใหม่ไม่ได้ถูก “กัด” ออกจากบล็อกซิลิกอน แต่ถูกประกอบ—เหมือนเค้กชั้นจิ๋ว—โดยการเพิ่มฟิล์มบาง ๆ ทำแพตเทิร์น และลบสิ่งที่ไม่ต้องการ ทำซ้ำร้อยครั้ง คุณจะได้ทรานซิสเตอร์ เส้นสื่อ และชั้นฉนวนที่เรียงซ้อนและสานกันเป็น 3 มิติ

ในภาพรวม การผลิตชิปวนรอบเป็นจังหวะที่คุ้นเคย:

แต่ละรอบสร้างหนึ่ง “ชั้นตัด” ของอุปกรณ์สุดท้าย—โครงสร้างเกต, รูติดต่อ, หรือสายเชื่อมต่อ—จนตรรกะและหน่วยความจำปรากฏจากสแต็ก

เมื่อฟีเจอร์วัดเป็นนาโนเมตรหลักตัวเดียว การควบคุมความหนาและรูปร่างไม่ใช่เรื่อง “ดีถ้ามี” อีกต่อไป ฟิล์มที่หนาเกินไปเล็กน้อยอาจปิดช่องแคบ; การกัดที่รุนแรงเกินไปอาจขยายเส้นหรือละเมิดชั้นด้านล่าง การเปลี่ยนแปลงโปรไฟล์เล็กน้อย—มุมผนังด้านข้าง, มุมโค้ง, ความหยาบผิว—สามารถเปลี่ยนการไหลของไฟฟ้าได้

การผลิตถูกจัดเป็น ขั้นตอนกระบวนการ (การดำเนินการ deposition/etch เฉพาะ) ที่ต้องทำงานภายใน หน้าต่างกระบวนการ—ช่วงค่าที่ผลลัพธ์ยังยอมรับได้ เมื่อชิปหนาแน่นขึ้น หน้าต่างเหล่านี้จะแคบลง และเพราะชั้นหลังขึ้นต่อชั้นก่อน การเบี่ยงเบนเล็กน้อยสามารถลุกลามเป็นการเยื้อง, ลัดวงจร, ขาดการเชื่อมต่อ และท้ายที่สุดคือผลผลิตที่ลดลง

Deposition คือครึ่งของการผลิตชิปที่เป็น “การเพิ่มวัสดุ”: สร้างฟิล์มบางมากบนเวเฟอร์เพื่อให้ขั้นตอนถัดไปสามารถทำแพตเทิร์น ปกป้อง หรือแยกไฟฟ้าในสิ่งที่อยู่ด้านล่าง ฟิล์มเหล่านี้ไม่ใช่ของตกแต่ง—แต่ละชั้นถูกเลือกมาเพื่อหน้าที่เฉพาะ และต้องทำงานได้เชื่อถือได้ทั่วทั้งฟีเจอร์จิ๋วจำนวนพันล้านชิ้น

Chemical Vapor Deposition (CVD) ใช้ก๊าซที่ทำปฏิกิริยาจนเกิดฟิล์มบนพื้นผิวเวเฟอร์ ใช้กันแพร่หลายสำหรับไดอิเล็กทริกและบางชั้นตัวนำ เพราะครอบคลุมพื้นที่กว้างได้มีความสม่ำเสมอดี

Physical Vapor Deposition (PVD) (มักเรียก “sputtering”) กระแทกอะตอมออกจากเป้าทำให้ตกลงบนเวเฟอร์ PVD นิยมใช้กับโลหะและวัสดุ hardmask โดยเฉพาะเมื่อคุณต้องการฟิล์มหนาแน่น แต่จะยากเมื่อจะเคลือบผนังข้างของโครงสร้างลึกและแคบมาก

Atomic Layer Deposition (ALD) ฝากวัสดุทีละโมเลกุลผ่านปฏิกิริยาพื้นผิวที่จำกัดตัวเอง ช้า แต่เด่นเมื่อการควบคุมและการคลุมพื้นที่สำคัญกว่าความเร็ว—โดยเฉพาะในฟีเจอร์ 3 มิติที่แคบที่สุด

เมื่อชิปย้ายไปสู่ฟิน, ทรัช, และรูแนวตั้ง การฝากชั้นไม่ได้เป็นปัญหาแค่ “ทาส่วนบน” อีกต่อไป Conformality บรรยายว่าฟิล์มเคลือบได้สม่ำเสมอแค่ไหน บนพื้นผิวด้านบน, ผนังด้านข้าง และก้น ของฟีเจอร์

ถ้าชั้นบางบนผนังด้านข้างหรือตีบที่ปาก เปิดช่องได้ไฟฟ้ารั่ว, เติมไม่สมบูรณ์ หรือพังในขั้นตอนกัดต่อไป Conformality สูงเป็นสิ่งจำเป็นสำหรับฟีเจอร์ลึกและแคบที่มีมาร์จิ้นน้อย

แม้ว่าความหนาจะถูกต้อง ฟิล์มต้องมีคุณสมบัติจริง ๆ:

ที่ชั้นนำ การฝากชั้นไม่ใช่แค่ “เพิ่มฟิล์ม” แต่มันคือวิศวกรรมวัสดุที่ละเอียด ถูกปรับจูนเพื่อให้การกัดและการแพตเทิร์ดถัดไปทำงานได้คาดการณ์ได้

Etch คือครึ่งลบของการผลิตชิป: หลังจากฟิล์มถูกวางและแพตเทิร์นด้วยเรซิสต์ การกัดจะเอาวัสดุที่เปิดออกเพื่อถ่ายทอดรูปแบบลงในชั้นด้านล่าง เคล็ดลับคือคุณไม่ค่อยต้องการเอาทุกอย่างออก—คุณต้องการเอา วัสดุหนึ่งอย่าง อย่างรวดเร็วขณะ หยุดบนอีกชั้นหนึ่ง คุณสมบัตินี้เรียกว่า selectivity ซึ่งเป็นเหตุผลว่าทำไม fabs ชั้นนำลงทุนมากในการรู้กระบวนการกัด (และทำไมผู้ขายเครื่องมืออย่าง Lam Research ใช้เวลาหลายปีในการปรับปรุงมัน)

สแต็กสมัยใหม่อาจมีซิลิกอน, ซิลิกอนไดออกไซด์, ซิลิกอนไนไตรด์, โลหะ และ hard masks ระหว่างการกัด คุณอาจต้องการเคลียร์ชั้นหนึ่งให้สะอาดในขณะที่คงชั้นที่เป็น etch-stop ไว้ Selectivity ที่ไม่ดีสามารถทำให้ชั้นสำคัญบางลง เปลี่ยนมิติทรานซิสเตอร์ หรือสร้างเส้นทางรั่วที่ทำให้ผลผลิตลดลง

การกัดขั้นสูงส่วนใหญ่ใช้ พลาสมา: ก๊าซความดันต่ำถูกให้พลังงานจนเกิดเป็นสปีชีส์ที่ทำปฏิกิริยา

เกิดสองอย่างพร้อมกัน:

การบาลานซ์ทั้งสองด้านคือศิลป์: เคมีมากเกินไปจะกัดใต้สลัก; ไอออนมากเกินไปอาจทำลายสิ่งที่คุณพยายามรักษาไว้

ทีมกระบวนการมักไล่ตามผลลัพธ์บางอย่าง:

แม้สูตรจะ “ถูก” เวเฟอร์จริงก็ยังต่อต้าน:

ที่โหนดชั้นนำ การจัดการรายละเอียดเหล่านี้มักคือความต่างระหว่างเดโมในห้องทดลองกับการผลิตจำนวนมาก

เมื่อคนคิดถึงการสเกลชิป มักนึกถึงเครื่องมือชิ้นเดียวที่ “พิมพ์” เส้นเล็กลง ในความเป็นจริง การถ่ายโอนแพตเทิร์นถูกจำกัดโดยทั้งห่วงโซ่—เรซิสต์, hardmasks, selectivity ของการกัด, ความเค้นของฟิล์ม, และการล้าง—ไม่ใช่แค่เครื่องไม้เครื่องมือชิ้นเดียว

Photoresist ดีในการจับแพตเทิร์น แต่โดยปกติจะบางและบอบบางเกินกว่าจะทนการกัดที่ลึกและแม่นยำในอุปกรณ์สมัยใหม่ ดังนั้น fabs จึงสร้าง hardmask stacks—ฟิล์มที่เลือกมาอย่างระมัดระวังวางบนชั้นเป้าหมาย

ลำดับการทำงานโดยสังเขป:

แต่ละฟิล์มที่ฝากถูกเลือกไม่ใช่แค่เพราะเป็นวัสดุอะไร แต่เพราะพฤติกรรมในขั้นตอนกัดถัดไป: ความเร็วการกัดเมื่อเทียบกับชั้นข้างเคียง, ความหยาบที่สร้าง, และการคงรูปได้ดีแค่ไหน

เมื่อมิติสำคัญเล็กลงเกินกว่าที่ลิโธกราฟีครั้งเดียวจะนิยามได้อย่างน่าเชื่อถือ fabs ใช้ multi-patterning—แยกลายหนาแน่นหนึ่งชุดเป็นหลายการเปิดรับและการถ่ายโอน นั่นไม่ได้เพิ่มแค่ขั้นตอนลิโธกราฟี มันทวีคูณวงรอบการฝาก/กัดสนับสนุนสำหรับ spacer, mandrel, trims, และ cut masks

ประเด็นคือ: “แพตเทิร์น” บนชิปชั้นนำนั้นอาจเป็นผลมาจาก หลายรอบ ของการฝากฟิล์มและการกัดกลับภายใต้อำนาจการควบคุมแน่นหนา

เพราะทุกขั้นตอนเปลี่ยนเงื่อนไขเริ่มต้นสำหรับขั้นตอนถัดไป ผลลัพธ์ที่ดีที่สุดมาจากการปรับจูนลำดับทั้งหมด—วัสดุ, สภาพพลาสมา, ความสะอาดของห้อง, และการล้าง—เป็นระบบเดียว การปรับปรุงเล็กน้อยในการกัดขั้นหนึ่งอาจถูกลบหรือขยายโดยการฝากขั้นถัดไป ซึ่งเป็นเหตุผลว่าทำไมความรู้การผสานกระบวนการจึงกลายเป็นจุดต่างเมื่อเวลาผ่านไป

ทรานซิสเตอร์แบบแผ่นเรียบเคยเป็น “แบน” ซึ่งทำให้หลายขั้นตอนรู้สึกเหมือนทาสีและตัดแต่งพื้นผิว การสเกลผลผลักให้วงการเข้าสู่ 3 มิติ: เริ่มจาก FinFETs (ฟินแนวตั้งที่เกตหุ้ม) และตอนนี้เป็นแนวคิด gate-all-around (GAA) ที่เกตล้อมช่องทางอย่างเต็มรูปแบบ (มักเป็นสแต็กของ nanosheets)

เมื่อฟีเจอร์มีผนังด้านข้าง มุม และหลุมลึก การฝากชั้นไม่ใช่แค่ “เคลือบด้านบน” อีกต่อไป ฟิล์มต้อง conformal—หนาเท่า ๆ กันที่ก้นทรัชและบนผิว นั่นคือเหตุผลที่เทคนิคอย่าง ALD และ CVD ที่ปรับจูนมาดีมีความสำคัญมากขึ้นที่ชั้นนำ: สองสามอะตอมที่บางเกินไปบนผนังด้านข้างอาจกลายเป็นความต้านสูง การเชื่อถือได้แย่ หรือตัวกั้นอ่อนที่ปล่อยให้วัสดุแพร่

การกัดต้องสร้าง โปรไฟล์ ที่ถูกต้อง: ผนังตรง ก้นสะอาด หยาบน้อย และการลบวัสดุเฉพาะโดยไม่กัดชั้นด้านล่าง ในแพตเทิร์น 3 มิติหนาแน่น การกัดเกินนิดเดียวอาจตัดชิ้นส่วนสำคัญ ในขณะที่กัดไม่พอทิ้งคราบที่ขวางการฝากถัดไป

โครงสร้างสมัยใหม่หลายอย่างมี อัตราส่วนสูง—ลึกมากเมื่อเทียบกับความกว้าง การได้ผลลัพธ์สม่ำเสมอทั่วพันล้านฟีเจอร์เหล่านี้ยากเพราะตัวถูกทำปฏิกิริยา ไอออน และของเสียเคลื่อนที่เข้าออกพื้นที่แคบไม่สม่ำเสมอ ปัญหาเช่น microloading และความเสียหายผนังด้านข้างมีโอกาสเกิดมากขึ้น

GAA และอินเตอร์คอนเน็กต์ขั้นสูงนำสแต็กวัสดุที่ซับซ้อนและอินเตอร์เฟซบางมากขึ้น นั่นเพิ่มมาตรฐานสำหรับ การเตรียมพื้นผิว: การล้างก่อน, การรักษาพลาสมาที่อ่อนโยน, และการควบคุมอินเตอร์เฟซก่อนฝากขั้นต่อไป เมื่อ “พื้นผิว” หนาเพียงไม่กี่ชั้นอะตอม ความรู้กระบวนการคือความต่างระหว่างอุปกรณ์ที่ใช้งานได้และอุปกรณ์ที่ล้มเหลวอย่างเงียบ ๆ ในเวลาต่อมา

“ผลผลิต” คือสัดส่วนของชิปบนเวเฟอร์ที่ทำงานตามต้องการ ถ้าเวเฟอร์มีไดหลายพันชิ้น การเปลี่ยนแปลงเพียงเล็กน้อยในอัตราข้อบกพร่องสามารถแปลเป็นชิ้นที่ขายได้เพิ่มหรือหายนับร้อย นั่นคือเหตุผลที่ผู้ผลิตหมกมุ่นกับตัวเลขเล็ก ๆ—เพราะเมื่อขยายแล้วการปรับปรุงเล็ก ๆ กลายเป็นผลผลิตที่แท้จริง

ข้อบกพร่องหลายอย่างมองไม่เห็นชัดใต้กล้องจุลทรรศน์ แต่แสดงผลเป็นความล้มเหลวทางไฟฟ้า ตัวอย่างทั่วไป:

ขั้นตอนการฝากและกัดมีอิทธิพลต่อทั้งหมดนี้ ฟิล์มที่เบี่ยงเบนเล็กน้อยในความหนา องค์ประกอบ หรือความสม่ำเสมออาจยังดู “ดี” แต่เปลี่ยนพฤติกรรมทรานซิสเตอร์พอที่จะหลุดจากเป้าความเร็วหรือการใช้พลังงาน

แม้จะไม่มีข้อบกพร่องชัดเจน แต่ความแปรปรวน ระหว่างตำแหน่งบนเวเฟอร์ (หรือระหว่างเวเฟอร์) ทำให้อุปกรณ์ทำงานไม่เหมือนกัน มุมหนึ่งร้อนกว่า มุมหนึ่งช้ากว่า ทำให้การแบ่งเกรดสินค้าเปลี่ยนหรือชิ้นล้มเหลว การควบคุมอัตราฝาก, สภาพพลาสมา, และ selectivity ของการกัดอย่างเข้มงวดช่วยลดการเปลี่ยนแปลงเหล่านี้

โรงงานทันสมัยไม่ได้ปรับจูนกระบวนการจากสัญชาตญาณ พวกเขาพึ่งพา เมโทรโลยี (วัดความหนา มิติวิกฤต โปรไฟล์ ความสม่ำเสมอ) และ การตรวจสอบ (ค้นหาฝุ่น ข้อบกพร่องแพตเทิร์น ปัญหาขอบ) ผลลัพธ์จะป้อนกลับสู่การปรับกระบวนการ:

ในเชิงปฏิบัติ นี่ยังสร้างปัญหาด้านซอฟต์แวร์: การผสานข้อมูลจากเครื่องมือ เมโทรโลยี และการตรวจสอบให้เป็นสิ่งที่วิศวกรจะลงมือได้อย่างรวดเร็ว ทีมมักสร้างแดชบอร์ดภายใน การเตือน และเครื่องมือ “อะไรเปลี่ยน?” เพื่อย่นเวลาจากสัญญาณถึงการแก้ไข แพลตฟอร์มอย่าง Koder.ai สามารถช่วยที่นี่โดยให้ทีมกระบวนการและข้อมูลสร้างเว็บแอปน้ำหนักเบาจากแชท—มีประโยชน์สำหรับผสาน KPI ผลผลิต บันทึกเหตุการณ์ และประวัติการรัน โดยไม่ต้องรอวงจรการพัฒนาที่ยาวนาน

ความรู้ที่มีค่าที่สุดเกิดจากพัฒนาการเล็ก ๆ ทุกครั้ง: ทุกโหนดสอนว่าอะไรทำให้เกิดข้อบกพร่องบางอย่าง การตั้งค่าใดล้มเหลวเมื่อเวลาผ่านไป และการรวมกันใดที่เสถียร บทเรียนเหล่านี้ส่งต่อ—ดังนั้นโหนดถัดไปจึงเริ่มด้วยเพลย์บุ๊กที่ดีกว่า ไม่ใช่แผ่นเปล่า

เครื่องมือ deposition หรือ etch ไม่ได้ทำงานด้วย “การตั้งค่า” เดียว แต่มันทำงานด้วย สูตร—ลำดับขั้นตอนที่กำหนด วิธี ที่กระบวนการทำในช่วงเวลา สูตรอาจรวมหลายเฟส (stabilize, pre-clean, main step, post-treatment) แต่ละเฟสมีการไหลของก๊าซ ความดัน อุณหภูมิ กำลัง RF เวลา และตรรกะจุดสิ้นสุด มันยังรวมรายละเอียดเงียบ ๆ: เวลา purge, พฤติกรรมการจับเวเฟอร์, และการเตรียมห้องก่อนเวเฟอร์แรก

เมื่อชิปย้ายสู่โหนดใหม่ fabs แนะนำวัสดุและรูปร่าง 3 มิติใหม่ ๆ—มักเกิดพร้อมกัน ฟิล์มที่ใช้ได้บนพื้นผิวแบนอาจทำงานต่างออกไปบนฟีเจอร์ลึก แรงกัดที่พอจะเป็น selective ในรุ่นก่อนอาจเริ่มทำลาย liner หรือ barrier ใหม่ นั่นคือเหตุผลที่สูตรวิวัฒนาการ: เป้าหมายอุปกรณ์เปลี่ยน (ความเร็ว พลังงาน ความเชื่อถือได้) รูปร่างแคบลง และข้อจำกัดการผสานเพิ่มขึ้น การพัฒนากระบวนการกลายเป็นวงจรการปรับจูน วัด และปรับซ้ำเป็นเวลานาน—บางครั้งแก้ปัญหาที่ปรากฏเฉพาะหลังจากพันเวเฟอร์

ในการผลิตจำนวนมาก ไม่พอที่ห้องเดียวจะได้ผลลัพธ์ดีครั้งเดียว ความทำซ้ำได้ คือสูตรเดียวกันให้ผลลัพธ์เดิมซ้ำแล้วซ้ำอีกสำหรับทุกเวเฟอร์ การจับคู่เครื่อง-to-เครื่อง คือสูตรที่ย้ายไปยังเครื่องอื่นยังให้ความหนา โปรไฟล์ และความสม่ำเสมอในขอบเขตแคบ—ถ้าไม่เช่นนั้น การวางแผนการผลิตและผลผลิตจะได้รับผลกระทบ

การควบคุมมลภาวะเป็นส่วนหนึ่งของความจริงนี้ ห้อง “แก่” เมื่อฟิล์มสะสมบนพื้นผิวภายในที่เปลี่ยนสภาพพลาสมาและความเสี่ยงอนุภาค Fabs พึ่งพาการเตรียมห้อง (chamber conditioning), การรัน seasoning, การล้าง และตารางบำรุงรักษาเชิงป้องกันเพื่อให้กระบวนการคงตัวเมื่อเวลาผ่านไป ความรู้ทางปฏิบัติการนี้—วิธีรักษาสูตรให้ทำงานได้เป็นเดือน ไม่ใช่เป็นนาที—คือที่ที่ประสบการณ์ทบเพิ่ม

ชิปชั้นนําไม่ได้ถูกผลิตโดยแค่ซื้อเครื่อง ติดตั้ง แล้วกด “run” ขั้นตอน deposition และ etch ถูกผูกอย่างแน่นกับเลย์เอาต์วัสดุสแต็ก และเป้าหมายความเชื่อถือได้ ดังนั้นคนที่สร้างอุปกรณ์และคนที่ดูแลโรงงานจึงมักทำงานวนไปมา

ผู้ออกแบบชิปกำหนดโครงสร้างที่ต้องการ ทีมผสานกระบวนการในโรงงานจะแปลการออกแบบนั้นเป็นลำดับ: ฝากชั้นนี้ ทำแพตเทิร์น กัด ล้าง ทำซ้ำ ผู้ผลิตเครื่องมือเช่น Lam Research จะช่วยเปลี่ยนความต้องการเหล่านั้นเป็นสูตรที่ใช้ได้จริงบนฮาร์ดแวร์

การส่งมอบนี้กลายเป็นลูป: การรันแรก ๆ เผยปัญหา (โปรไฟล์เลว, คราบ, ขอบลายหยาบ, ความเสียหายที่ไม่คาดคิด) และข้อมูลย้อนกลับจะกลับไปทั้ง flow กระบวนการและการตั้งค่าเครื่อง—บางครั้งถึงระดับฮาร์ดแวร์ เช่น วัสดุห้อง, แหล่งพลาสมา, หรือการจ่ายแก๊ส

ที่ชั้นนำ คุณไม่สามารถปรับอัณฑะ deposition หรือ etch แยกจากกันเพราะแต่ละขั้นเปลี่ยนเงื่อนไขเริ่มต้นสำหรับขั้นถัดไป การเคลื่อนไหวเล็ก ๆ ในความหนาฟิล์มสามารถเปลี่ยนอัตราการกัด การกัดที่รุนแรงขึ้นอาจทำให้การฝากถัดไปไม่ conformal การปรับจูนร่วมกันจะสอดคล้องระหว่าง:

Fabs ต้องถ่วง throughput vs. precision เสมอ: การประมวลผลเร็วขึ้นอาจเพิ่มความแปรปรวน ขณะที่การควบคุมแน่นอาจลดเวเฟอร์ต่อชั่วโมง เช่นเดียวกับ selectivity vs. damage: การกัดที่เลือกวัสดุได้ดีอาจต้องเงื่อนไขที่รุนแรงขึ้นซึ่งเสี่ยงต่อความหยาบหรือข้อบกพร่อง

คุณค่าสำคัญที่มอบให้คือการสนับสนุนการผสานอย่างต่อเนื่อง—การแก้ปัญหาในไซต์, การจับคู่ประสิทธิภาพข้ามห้อง, ลดการเกิดเหตุ, และช่วยฟื้นฟูเมื่อผลผลิตเปลี่ยน สำหรับการผลิตจำนวนมาก ความร่วมมือนี้อาจสำคัญเท่ากับสเปคของเครื่อง

“การทบเพิ่ม” ในการผลิตชิปไม่ได้หมายถึงแค่การซื้อเครื่องดีขึ้น แต่มันคือวิธีที่ข้อได้เปรียบเล็ก ๆ สะสมเมื่อทีมรันกระบวนการประเภทเดียวกัน—deposition และ etch—ซ้ำ ๆ ข้ามหลายโหนด

ในบริบทนี้ การทบเพิ่มคือวงล้อของ:

ไม่มีสิ่งใดรับประกันความสำเร็จ แต่โดยปกติจะย่นเวลาจาก “ใช้งานได้ในเดโม” ไปสู่ “ใช้งานได้ทุกวันในการผลิต”

เมื่อ fab ขยับโหนดใหม่ มักเจอปัญหาที่คาดไว้: ความแปรปรวน ข้อบกพร่อง กรณีขอบ และการจับคู่เครื่อง ทุกปัญหาที่แก้ได้สร้างความรู้ที่นำกลับมาใช้ซ้ำได้—วิธีปรับสภาพพลาสมาโดยไม่ทำลายชั้นบอบบาง, การล้างห้องแบบไหนป้องกันการพุ่งของอนุภาค, หรือวิธีตรวจจับการดริฟท์ก่อนจะกลายเป็นการเสียผลผลิต

เมื่อเวลาผ่านไป วงจรการเรียนรู้เหล่านี้ทำให้การขยับโหนดต่อไปราบรื่นกว่า ทีมเริ่มใกล้จุดหมายเพราะพวกเขาได้ทำแผนที่กับดักไว้แล้ว

แม้ว่าวิธีอื่นจะดูคล้ายกันบนกระดาษ การเปลี่ยนจริงอาจมีค่าใช้จ่ายและเสี่ยง:

นั่นคือเหตุผลว่าทำไมความรู้การผลิตมักคงอยู่และเติบโต: เมื่อ flow เสถียร แรงจูงใจคือปรับปรุง ไม่ใช่เริ่มใหม่ เว้นแต่ผลประโยชน์จะคุ้มค่ากับการเรียนรู้ใหม่

เครื่องมือ deposition หรือ etch อาจดูน่าประทับใจบนแผ่นสเปค—จนกว่าจะต้องรัน 24/7 บนพันเวเฟอร์ด้วยผลลัพธ์เดิม ในการผลิตจำนวนมาก ความเชื่อถือได้และเวลาทำงานไม่ใช่แค่ “ดีถ้ามี” มันกำหนดจำนวนเวเฟอร์ดีที่โรงงานส่งออกได้

Deposition และ etch อยู่ได้หรือตายด้วยความเสถียรของกระบวนการ การดริฟท์เล็ก ๆ ใน การไหลก๊าซ, ความดันห้อง, กำลังพลาสมา, หรืออุณหภูมิ สามารถเปลี่ยนความหนาฟิล์ม มุมผนัง หรือระดับความเสียหาย—เปลี่ยนสูตรที่เคยทำงานให้กลายเป็นการเสียผลผลิต นั่นคือเหตุผลที่เครื่องชั้นนำ (รวมถึงระบบของ Lam Research) ลงทุนในฮาร์ดแวร์ที่ทำซ้ำได้: การส่ง RF ที่เสถียร, การควบคุมการไหลมวลที่แม่นยำ, การจัดการความร้อน, และเซ็นเซอร์ที่จับการเบี่ยงเบนได้เร็ว

แม้กระบวนการจะสมบูรณ์ ผลการผลิตก็เสียเมื่อเครื่องมีเวลาหยุดบ่อย ผลผลิตจริงของโรงงานถูกกำหนดโดย:

เครื่องมือที่ซ่อมบำรุงง่ายกว่า—และได้รับการสนับสนุนด้วยการพยากรณ์อะไหล่ที่ดี—จะทำให้ห้องทำงานได้มากขึ้นและล็อตเคลื่อนที่ได้ต่อเนื่องขึ้น

เวลาทำงานสูงมักลด ต้นทุนต่อเวเฟอร์: ผู้ปฏิบัติงานไม่ต้องนั่งเฉย ๆ พื้นที่คลีนรูมใช้งานได้ดีขึ้น และเวลาที่ใช้แก้ไขลดลง ที่สำคัญ การมีพร้อมใช้งานสม่ำเสมอยังทำให้ตารางการส่งมอบคาดเดาได้ ซึ่งสำคัญเมื่อขั้นตอนถัดไปต่อคิวแน่น

อีกความจริงหนึ่ง: การขยับจากเดโมในห้องทดลองสู่การผลิตจำนวนมาก ทดสอบเครื่องต่างออกไป การรันยาว การเพิ่มอัตราเริ่มเวเฟอร์ และงบประมาณข้อบกพร่องที่เข้มงวดเปิดจุดอ่อนได้เร็ว—ดังนั้นวิศวกรรมความเชื่อถือได้เป็นส่วนสำคัญของ “ความสามารถของกระบวนการ”

เมื่อชิปผลักเข้าโหนดเล็กลงและโครงสร้าง 3 มิติยิ่งขึ้น ความก้าวหน้าขึ้นอยู่กับการทำซ้ำขั้นตอน deposition และ etch อย่างแม่นยำ—บ่อยครั้งเป็นร้อยครั้งในสแต็กอุปกรณ์เดียว คอขวดถัดไปมักไม่ใช่การค้นพบเดียว แต่คือความยากสะสมในการทำให้ทุกวงรอบสม่ำเสมอ ในขณะเดียวกันต้องรักษาผลผลิต ควบคุมความแปรปรวน และเร่งการขยับโหนดให้เร็วพอ

แนวโน้มหลายอย่างจะกดดัน deposition/etch มากที่สุด:

เมื่อเปรียบเทียบผู้ขายเครื่องมือหรือแนวทาง fab (รวมถึง Lam Research และคู่แข่ง) ให้มองที่ผลลัพธ์:

หากต้องการลงลึก ดูบทความอธิบายที่เกี่ยวข้องบน /blog หากคุณกำลังประเมินตัวเลือก—หรือสร้างเครื่องมือภายในเพื่อวิเคราะห์ผลผลิต เหตุการณ์ และเมตริกรัน—ดู /pricing สำหรับวิธีคิดเรื่องต้นทุน ความเร็ว และความสามารถ (รวมถึงเมื่อแพลตฟอร์มสร้างด้วยแชทอย่าง Koder.ai สามารถแทนที่ระบบซอฟต์แวร์เดิมที่ช้ากว่าได้)

Deposition คือขั้นตอน “เพิ่ม”: เครื่องมือจะวางฟิล์มบางมาก ๆ (โลหะ, ไดอิเล็กทริก, ชั้นกั้น, liners, hardmask) บนเวเฟอร์ ส่วน Etch คือขั้นตอน “ลบ”: เครื่องมือจะแกะวัสดุเฉพาะเจาะจงเพื่อนำรูปแบบไปสู่ชั้นด้านล่างและสร้างฟีเจอร์ต่าง ๆ

การสเกลขึ้นอยู่กับการควบคุม ความหนา รูปร่าง และอินเตอร์เฟซ ในมิติระดับนาโนเมตร ดังนั้นคุณภาพของการ deposition/etch จึงส่งผลโดยตรงต่อประสิทธิภาพและผลผลิต

“Leading-edge” โดยทั่วไปหมายถึงโหนดการผลิตที่ก้าวหน้าที่สุดในระดับการผลิตจำนวนมาก—ที่ซึ่งโครงสร้างอุปกรณ์และวัสดุใหม่ ๆ ปรากฏขึ้นก่อน และความคลาดเคลื่อนที่ยอมรับได้แคบมาก

มันไม่ใช่แค่ตัวเลขการตลาด แต่คือการทำงานด้วย หน้าต่างกระบวนการที่เล็กลง และความไวต่อความเปลี่ยนแปลงเล็ก ๆ สูงขึ้น

เพราะชิปสมัยใหม่ถูกสร้างขึ้นด้วยการวนรอบซ้ำ ๆ ดังนี้:

เมื่อตัวเลขมิติเล็กลงและสแตกซับซ้อนขึ้น หนึ่ง “ชั้น” มักต้องการ เพื่อให้ได้มิติและโปรไฟล์ที่ต้องการ

Conformality คือการที่ฟิล์มเคลือบได้เท่ากันบน ด้านบน, ผนังด้านข้าง, และก้น ของฟีเจอร์ 3 มิติ

มันสำคัญเพราะการเคลือบไม่สม่ำเสมออาจ:

เทคนิคอย่าง ALD มักถูกใช้เมื่อจำเป็นต้องการ conformality สูง

Selectivity คือความเร็วที่การกัดเอาวัสดุหนึ่งออกได้เร็วกว่าอีกวัสดุหนึ่ง (มักเทียบกับชั้นที่เป็น “etch stop”)

Selectivity สูงช่วยให้:

Photoresist มักบางและบอบบางเกินกว่าจะทนการกัดลึกและแม่นยำแบบสมัยใหม่ได้ดี ดังนั้น fabs จึงใช้ hardmask stack เพื่อทำหน้าที่เป็น “ล่าม” ที่ทนทานกว่าระหว่างลายจาก resist และชั้นเป้าหมาย

ลำดับทั่วไปคือ:

การเลือก hardmask ขึ้นกับ

Multi-patterning แบกลายแน่นหนึ่งชุดเป็นหลายขั้นตอนเมื่อการพิมพ์ครั้งเดียวไม่สามารถกำหนดพิตช์สุดท้ายได้เชื่อถือได้

นั่นเพิ่มขั้นตอนสนับสนุน เช่น การสร้าง spacer หรือ mandrel ซึ่งเพิ่มจำนวนการทำ deposition + etch (รวมถึงการล้างและเมโทรโลยี) ที่ต้องใช้ในการสร้างฟีเจอร์สุดท้ายหนึ่งชุด

ฟีเจอร์อัตราส่วนสูง (สูงมากเมื่อเทียบความลึกต่อความกว้าง) ทำให้การขนส่งสารทำได้ยากขึ้น:

ผลคือความเสี่ยงต่อปัญหาโปรไฟล์ (notching/footing), เศษตกค้าง, ความหยาบ และความแปรปรวนเพิ่มขึ้น—ทำให้การปรับจูนกระบวนการต้องเข้มงวดกว่าเดิม

ผลผลิต (yield) คือสัดส่วนของไดบนเวเฟอร์ที่ใช้งานได้ การฝากและการกัดมีผลต่อผลผลิตโดยก่อให้เกิดข้อบกพร่องและความแปรปรวนที่กลายเป็นความล้มเหลวทางไฟฟ้า เช่น:

แม้การเบี่ยงเบนเล็ก ๆ ในความหนาหรือโปรไฟล์ก็สามารถผลักอุปกรณ์ให้ออกนอกสเปกได้ที่โหนดชั้นนำ

สาเหตุที่ความรู้ด้านการผลิต “ทบเพิ่ม” คือความแตกต่างในกระบวนการผลิตไม่ได้อยู่แค่สเปคของเครื่อง แต่เป็น ความรู้เชิงปฏิบัติ: สูตรการทำงาน, ลำดับการผสาน, การเรียนรู้ข้อบกพร่อง และการจับคู่เครื่อง

ความรู้นี้ทบเพิ่มเพราะโหนดใหม่สร้างจากบทเรียนก่อนหน้าเกี่ยวกับ:

นั่นคือเหตุผลที่บริษัทอุปกรณ์อย่าง มีความสำคัญเชิงกลยุทธ์ในการผลิตชิปขั้นนำ