04 May 2025·8 dk

Lam Research ve Çip Üretiminde Biriken Avantaj

Kaplama ve aşındırma araçlarının ileri düzey çipleri nasıl şekillendirdiği, süreç bilgisinin nesiller boyunca nasıl biriktiği ve bunun verim, düğümler ve ölçeklendirme için ne anlama geldiği.

Neden Kaplama ve Aşındırma Çip Ölçeklendirmesinin Merkezinde Duruyor

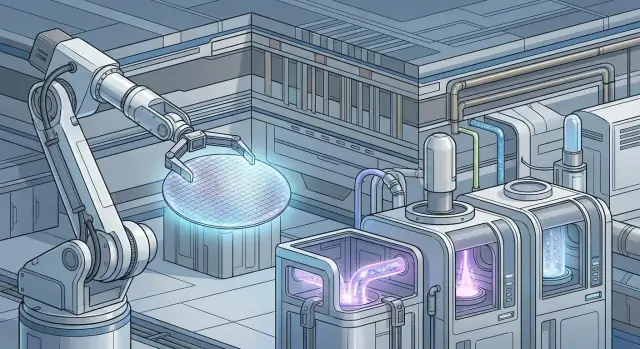

Çip üretimini en tekrarlanabilir hareketlere indirgerseniz, iki işlem sürekli tekrar eder: kaplama ve aşındırma.

Kaplama “ekleme” adımıdır. Araçlar wafer üzerine iletken, yalıtkan veya özel bariyer tabakaları gibi ultra-ince filmler bırakır—bazen sadece birkaç atom kalınlığında. Aşındırma ise “çıkarma” adımıdır. Araçlar, altında kalan katmanlara zarar vermeden, transistörler ve bağlantılar olacak minik yapıların ortaya çıkması için malzemeyi seçici şekilde kazır.

Çipler ölçeklendikçe, bu iki adım mühendislerin nanometre boyutlarında en çok önem verdiği üç şeyi kontrol etmek için kullandığı ana düğmeler haline geldi: kalınlık, şekil ve ara yüzler. İşte bu yüzden Lam Research gibi ekipman firmaları, ileri düzey üretimin kalbine yakın konumlanır.

“İleri düzey” gerçekte ne demek

“İleri düzey” genelde en gelişmiş, yüksek hacimli üretim düğümlerini ifade eder—burada yoğunluk, güç ve performans hedefleri en iddialıdır ve hata payı en küçüktür. Bu sadece pazarlama numarası değildir; yeni cihaz yapıları ve malzemeler ilk olarak burada ortaya çıkar.

Biriken (compounding) avantaj

Araç yeteneği önemlidir (uniformite, selektivite, zarar kontrolü, verim). Ama süreç bilgisi de en az bunun kadar önemlidir: reçeteler, entegrasyon taktikleri, metroloji geri bildirimi ve kusur öğrenimleri, harika bir aracı kararlı, yüksek verimli bir fabrika sürecine dönüştürür.

Bu avantaj teknoloji nesilleri boyunca birikir çünkü her yeni düğüm sıfırdan başlamaz—filmlerin nasıl büyüdüğüne, plazmanın nasıl davrandığına ve küçük varyasyonların nasıl büyük verim dalgalanmalarına yol açtığına dair önceki öğrenmelerin üzerine kurulur.

Sonraki bölümlerde neleri ele alacağız

Kaplama–aşındırma döngülerinin neden katlanarak arttığını görmek için şunlara bakacağız:

- Sınırda desenleme ve neden tekrarlayan “kapla–aşındır–temizle” döngülerinin yaygın olduğu

- 3B yapılar (yüksek en-boy oranlı özellikler) doldurması ve kazınması daha zor olanlar

- Verim öğrenimi, kusurlar ve değişkenlik—deneyimin paraya dönüştüğü yer

- Araç üreticileri ile fablar arasındaki geri besleme döngülerinin iyileşmeyi hızlandırması

Katmanlardan Mantığa: Modern Çipler Gerçekte Nasıl İnşa Edilir

Modern bir çip bir blok silikonun “işlenmesi” ile yaratılmaz. Daha çok mikroskobik bir kat kat pasta gibi monte edilir—ultra-ince filmler tekrar tekrar eklenir, desenlenir ve istemediğiniz bölümler seçici şekilde çıkarılır. Bunu yüzlerce kez yaparsanız, transistörler, bağlantılar ve yalıtkan bariyerler 3B olarak üst üste gelir ve iç içe geçer.

Tekrarlayan döngü: ekle, desenle, çıkar

Yüksek düzeyde, çip üretimi tanıdık bir ritimle döngüye girer:

- Kaplama bir film bırakır (metal, oksit, nitrit vb.), genellikle birkaç atomtan birkaç nanometreye kadar.

- Desenleme o filmin nerede kalacağını tanımlar (litografi ile bir maske oluşturulur).

- Aşındırma açıkta kalan bölgeleri kaldırır ve deseni filme geçirir.

Her döngü nihai cihazın bir “dilimini” oluşturur—kapı yapıları, kontak delikleri veya iletim hatları—ta ki çipin mantığı ve belleği yığından ortaya çıkana kadar.

Küçük özellikler neden aşırı kontrol gerektirir

Özellikler tek basamaklı nanometrelerle ölçüldüğünde, kalınlık ve şekil kontrolü “iyi olur” değil, zorunludur. Bir film biraz fazla kalınsa dar bir açıklığı kapatabilir; aşındırma biraz fazla agresifse bir hattı genişletebilir veya altında yatan katmana zarar verebilir. Yan duvar açısı, köşe yuvarlanması, yüzey pürüzlülüğü gibi küçük profil değişiklikleri bile elektriğin akışını etkileyebilir.

Süreç adımları, süreç pencereleri ve verim

Üretim, belirli kaplama/aşındırma işlemlerini içeren süreç adımlarına ayrılır ve bu adımların bir süreç penceresi içinde çalışması gerekir—sonuçların tutarlı biçimde kabul edilebilir olduğu ayar aralığı. Çipler yoğunlaştıkça bu pencereler küçülür. Ve çünkü sonraki katmanlar öncekinin üzerine kurulur, küçük bir sapma hizalanma hatalarına, kısa devrelere, kopmalara ve nihayetinde daha düşük verime yol açabilir.

Kaplama 101: Atom Seviyesinde Kontrol ile Film Koymak

Kaplama, çip üretiminin “malzeme ekleyen” yarısıdır: gelecek adımların altındaki yüzeyi korumak, desenlemek veya elektriksel olarak izole etmek için wafer üzerine ultra-ince filmler oluşturmak. Bu filmler dekoratif değildir—her biri belirli bir görev için seçilir ve milyarlarca küçük özellik boyunca güvenilir çalışması gerekir.

Üç ana yaklaşım: CVD, PVD ve ALD

Chemical Vapor Deposition (CVD), reaktif gazlar kullanarak wafer yüzeyinde katı bir film oluşturur. Büyük alanları verimli ve iyi uniformiteyle kaplayabildiği için dielektrikler ve bazı iletken katmanlarda yaygındır.

Physical Vapor Deposition (PVD) (çoğunlukla “sputtering”), hedef bir malzemeden atomları söküp wafer üzerine depozite eder. Metaller ve hardmask malzemeleri için yaygındır; sıkı, yoğun filmler üretir fakat çok derin, dar yapılarda yan duvarları kaplamakta zorlanabilir.

Atomic Layer Deposition (ALD), malzemeyi yüzeyde kendi kendini sınırlayan reaksiyonlarla bir moleküler “doz” halinde biriktirir. Daha yavaştır ancak kontrolün ve kaplamanın hızdan daha önemli olduğu, özellikle en sıkışık 3B özelliklerde mükemmeldir.

“Konformalite” ne demek (ve neden önemli)

Çipler finler, hendekler ve dikey deliklere doğru ilerledikçe, kaplama basit bir “üstü boyama” sorunu olmaktan çıkar. Konformalite, bir filmin üst yüzey, yan duvar ve dip bölgelerini ne kadar eşit kapladığını tarif eder.

Bir katman yan duvarda ince kalır veya açıklıkta tıkanma yaparsa, elektriksel kaçak, kötü dolum veya sonraki aşındırma adımlarında başarısızlık olabilir. Derin, dar özelliklerde yüksek konformalite çok az hata payı olduğu için kritiktir.

Verimi belirleyebilecek film özellikleri

Kalınlık doğru olsa bile film birkaç pratik gereksinimi karşılamalıdır:

- Uniformite: tüm waferda ve waferlar arasında tutarlı kalınlık.

- Safsızlıklar: istenmeyen atomlar elektriksel davranışı değiştirebilir veya güvenilirlik sorunları yaratabilir.

- Gerilme: çok çekme veya sıkıştırma gerilmesi yapılar warpage veya çatlamaya yol açabilir.

- Yapışma: katmanlar termal döngüler, temizlik ve aşındırma sırasında tutunmalıdır.

Sezgisel örnekler: bu katmanlar gerçekte ne iş yapar

- Linerlar özellik yan duvarlarını korur ve sonraki dolumlar için “başlangıç koşullarını” belirler.

- Bariyerler metalleri çevreleyen malzemelere difüze olmaktan alıkoyar (güvenilirlik için kritik).

- Hardmasklar fotoresisten daha agresif aşındırmaları atlatabilecek sağlam şablonlar gibi davranır.

- Dielektrik katmanlar iletkenleri elektriksel olarak izole eder—kısa devreleri önlemek için vazgeçilmezdir.

İleri düğümde kaplama sadece “film eklemek” değildir. Her bir sonraki aşındırma ve desenleme adımının öngörülebilir davranmasını sağlayacak şekilde hassas malzeme mühendisliğidir.

Aşındırma 101: Altındaki Şeye Zarar Vermeden Şekiller Kazımak

Aşındırma, kaplandıktan ve resist ile desenlendikten sonra açığa çıkan malzemeyi kaldırarak deseni alt katmana aktarmak için yapılan “çıkarma” işlemleridir. Hile şu ki genelde her şeyi kaldırmak istemezsiniz—bir malzemeyi hızlıca kaldırırken diğerini bırakmak istersiniz. Bu özellik selektivite olarak adlandırılır ve ileri düğüm fablarının aşındırma süreç bilgisine bu kadar yatırım yapmasının (ve Lam Research gibi tedarikçilerin yıllarını buna harcamasının) nedeni budur.

Selektivite neden önemlidir

Modern yığınlar silikon, silikon oksit, silikon nitrür, metaller ve hardmasklar içerebilir. Aşındırma sırasında bir katmanı temizlemek isteyebilirsiniz, aynı zamanda “etch stop” katmanını sağlam bırakmak istersiniz. Zayıf selektivite kritik katmanları inceltebilir, transistor boyutlarını kaydırabilir veya verimi düşüren kaçak yollar oluşturabilir.

Plazma aşındırma, kavramsal olarak

Çoğu ileri aşındırma bir plazma kullanır: düşük basınçlı gaz, reaksiyona giren türlere dönüştürülür.

Aynı anda iki şey olur:

- Kimya: reaktif radikaller hedef malzemeyle uçucu yan ürünler oluşturur (böylece pompalanıp uzaklaştırılabilirler).

- Yönsellik: elektrik alanları iyonları wafer yönünde hızlandırır, dar hendekleri ve kontakt deliklerini “düz aşağı” bileşeniyle oymaya yardımcı olur.

Bunları dengelemek sanattır: fazla kimya özellikleri altından oyabilir; fazla iyon enerjisi ise korunması gereken yüzeye zarar verebilir.

“İyi” bir aşındırma nasıl görünür

Süreç ekipleri genellikle şu hedefleri kovalar:

- Dikey yan duvarlar (özelliklerin istenen şekle uyması için)

- Minimum hasar (daha az yüzey pürüzlenmesi, daha az sıkışmış yük, daha az kristal bozulması)

- Tekrarlanabilir profiller waferdan wafera ve araçtan araca (böylece aşağı adımlar öngörülebilir davranır)

Yaygın aşındırma zorlukları

Reçete “doğru” olsa bile gerçek waferlar mücadele eder:

- Microloading: yoğun ve seyrek desen bölgeleri farklı hızlarda aşınır.

- Footing/notching: bir ara yüz veya etch-stop katmanı yakınında profil bozulması.

- Pürüzlülük: yan duvar dokusu direnci veya değişkenliği artırabilir.

- Kalıntılar: polimer veya yeniden biriken malzeme sonraki kaplama veya temizliği engelleyebilir.

İleri düğümlerde bu ayrıntıları yönetmek genellikle bir laboratuvar demodan yüksek hacimli üretime geçiş arasındaki farktır.

Sınırda Desenleme: Neden Aşındırma/Kaplama Döngüleri Çoğalıyor

Go from idea to deployment

İç web uygulamanız hazır olduğunda ekstra el değiştirmeye gerek kalmadan dağıtın ve barındırın.

İnsanlar çip ölçeklendirmesini genellikle daha küçük çizgileri “bastıran” tek bir mucize makine olarak hayal eder. Gerçekte desen aktarımı, resist, hardmasklar, aşındırma selektivitesi, film gerilmesi ve temizlik gibi tüm zincirle sınırlanır—tek bir sihirli araçla çözülmez.

Hardmask yığınları: bir desenin tercümana ihtiyacı vardır

Fotoresist deseni yakalamada iyidir ama genellikle modern cihazlarda gereken derin, hassas aşındırmaları atlatacak kadar kalın veya dayanıklı değildir. Bu yüzden fablar hardmask yığınları oluşturur—hedef katmanın üzerine depozite edilen dikkatle seçilmiş filmler.

Basitleştirilmiş akış şöyle görünür:

- Kapla bir veya daha fazla hardmask katmanı (çoğunlukla selektivite için farklı malzemeler).

- Aşındır resist desenini hardmask'e aktar.

- Aşındır hardmask desenini alttaki filme aktar.

- Strip/temizle, gerekirse tekrarla.

Her depozite edilen film sadece kendi kimliği için değil, bir sonraki aşındırma sırasında nasıl davranacağı—ne kadar hızlı aşındığı, ne kadar pürüz oluşturduğu ve şeklini ne kadar iyi koruduğu—göz önünde bulundurularak seçilir.

Çoklu desenleme (multi-patterning): bir özellik birçok adıma dönüşür

Kritik boyutlar tek bir litografi geçişinin güvenilir şekilde tanımlayamayacağı kadar küçüldüğünde, fablar multi-patterning kullanır—bir yoğun deseni bir dizi maruz bırakma ve aktarım adımına böler. Bu yalnızca litografi adımlarını eklemez; spacerlar, mandreller, trim ve cut maske gibi destekleyici kaplama/aşındırma döngülerini de çoğaltır.

Özet: bir ileri düğüm çipindeki “desen” genellikle sıkı kontrolde birkaç kapla ve aşındırma döngüsünün sonucu olabilir.

Uçtan uca ayar neden önemlidir

Çünkü her adım bir sonraki için başlangıç koşullarını değiştirir, en iyi sonuçlar tüm diziyi—malzemeleri, plazma koşullarını, oda temizliğini ve temizlemeleri—tek bir sistem olarak ayarlamaktan gelir. Bir aşındırmadaki küçük bir iyileşme bir sonraki kaplamayla silinebilir (veya büyütülebilir), bu yüzden süreç entegrasyonu bilgisi zamanla ayırt edici hale gelir.

3B Transistorler ve Yüksek En-Boy Oranları Zorluğu Artırır

Planar transistörler çoğunlukla “düz”tü ve birçok adımı bir yüzeyi boyamak ve kırpmak gibi hissettiriyordu. Ölçeklendirme endüstriyi 3B'ye itti: önce FinFET'ler (kenarı gate ile sarılmış dikey bir “fin”), şimdi ise gate-incen çevreleyen (GAA) ve genellikle yığılmış nanosheetler gibi yapılar.

3B neden kaplamayı değiştirir

Özelliklerin yan duvarları, köşeleri ve derin boşlukları olduğunda, kaplama basit bir “üstü kaplama” olmaktan çıkar. Filmler konformal olmalı—bir hendeğin dibinde neredeyse üst yüzeyle aynı kalınlıkta.

Bu yüzden ALD ve dikkatle ayarlanmış CVD adımları ileri düğümde daha fazla önem kazanır: yan duvarda birkaç atom eksikliği yüksek direnç, daha kötü güvenilirlik veya istenmeyen difüzyonla sonuçlanabilir.

3B neden aşındırmayı daha seçici yapar

Aşındırma doğru profili oluşturmak zorundadır: düz duvarlar, temiz dipler, minimum pürüzlülük ve bir malzemeyi kaldırırken diğerini yutmama. Yoğun 3B desenlerde küçük bir “over-etch” kritik bölgeleri tırnaklayabilir; “under-etch” ise sonraki kaplamayı engelleyecek kalıntı bırakır.

Yüksek en-boy oranı: uniformite tuzağı

Modern yapıların çoğu yüksek en-boy oranlı—dibi dar ama derin. Milyarları bulan bu özelliklerde uniform sonuçlar elde etmek zordur çünkü reaktifler, iyonlar ve artık ürünler dar alanlarda eşit hareket etmez. Microloading ve yan duvar hasarı gibi problemler daha olası hale gelir.

Yeni malzemeler, yeni yüzeyler demek

GAA ve gelişmiş interconnectler daha karmaşık malzeme yığınları ve ultra-ince ara yüzler getirir. Bu, yüzey hazırlığı için çıtayı yükseltir: ön temizlemeler, nazik plazma işlemleri ve bir sonraki kaplama adımından önce ara yüz kontrolü. “Yüzey” sadece birkaç atom tabakası kalınlığındaysa, süreç bilgisi çalışan bir cihaz ile sonradan sessizce arızalanan bir cihaz arasındaki fark olur.

Verim, Kusurlar ve Değişkenlik: Süreç Bilgisinin Paraya Dönüştüğü Yer

“Verim”, wafer üzerindeki çalışır durumda olan çiplerin payıdır. Eğer bir wafer binlerce çip taşıyorsa, kusur oranındaki küçük bir değişim yüzlerce satılabilir parçaya dönüşebilir. Bu yüzden üreticiler kulağa küçük gelen sayılar üzerinde takıntılıdır—çünkü ölçekte küçük iyileşmeler gerçek üretime dönüşür.

Kusurlar nasıl elektriksel problemlere dönüşür

Pek çok verim kaybı mikroskop altında dramatik görünmez; elektriksel arızalar olarak ortaya çıkar. Bazı yaygın örnekler:

- Opens: bir hat incelir veya kopar, akım akmaz.

- Shorts: ayrılması gereken iki özellik temas eder, istenmeyen bağlantı oluşur.

- Leakage: yalıtkan katmanlar çok ince, gözenekli veya hasarlı olur, akım “sızar”.

Kaplama ve aşındırma adımları bunların tümünü etkileyebilir. Kalınlığı, bileşimi veya uniformitesi biraz sapmış bir film “gözle görünür” iyi olsa bile transistor davranışını hız veya güç hedeflerinin dışına itebilir.

Değişkenlik: sessiz verim katili

Açık bir kusur olmasa bile wafer içi veya waferlar arasındaki varyasyon, cihazların tutarsız davranmasına yol açar. Bir köşe daha sıcak çalışır, bir köşe daha yavaş olur ve ürün sınıflandırması değişir—veya parça başarısız olur. Kaplama hızları, plazma koşulları ve aşındırma selektivitesinin sıkı kontrolü bu dalgalanmaları azaltır.

Metroloji ve muayene direksiyon simidi gibidir

Modern fablar süreçleri sezgiyle ayarlamaz. Onlar metroloji (kalınlık, kritik boyutlar, profil şekli, uniformite ölçümü) ve muayene (partikül, desen kusuru, kenar sorunları bulma) kullanır. Sonuçlar süreç ayarlarına geri besleme sağlar:

- Profiller kayarsa, aşındırma kimyası veya zamanı ayarlanır.

- Filmler kalınlık olarak değişirse, kaplama parametreleri düzeltilir.

- Kusur imzaları yükselirse, mühendisler kaynağı belirlemek için belirli bir modül, oda koşulu veya malzeme partisinden iz sürer.

Pratikte bu aynı zamanda bir yazılım sorunu da yaratır: araçlardan, metrolojiden ve muayenedan gelen verileri mühendislerin hızlıca kullanabileceği hale getirmek. Ekipler genellikle dahili panolar, alarm sistemleri ve “ne değişti?” araçları kurar ki sinyali düzeltmeye dönüştürme döngüsü kısalsın. Koder.ai gibi platformlar burada fayda sağlar; süreç ve veri ekiplerinin chat üzerinden hafif web uygulamaları üretmesine izin vererek uzun geleneksel geliştirme döngülerini atlatabilir.

Öğrenme düğümleri nesiller boyunca birikir

En değerli bilgi artımlıdır: her düğüm hangi kusurların hangi ayarlardan kaynaklandığını, hangi ayarların zamanla sürüklendiğini ve hangi kombinasyonların kararlı olduğunu öğretir. Bu dersler ileriye taşınır—böylece bir sonraki düğüm boş bir sayfa yerine daha iyi bir başlangıç kitabıyla başlar.

Reçeteler, Tekrarlanabilirlik ve Süreç Geliştirmenin Uzun Oyunu

Plan before you build

Kodlamadan önce Koder.ai Planning Mode ile bir dahili aracınızı planlayın.

Bir kaplama veya aşındırma aracı tek bir “ayar”la çalışmaz. O, sürecin zaman içinde nasıl gerçekleşeceğini tanımlayan yapılandırılmış bir reçete ile çalışır. Bir reçete birden fazla faz içerebilir (stabilize, ön-temizlik, ana adım, sonrası işlem), her biri kendi gaz akışları, basınç, sıcaklık, RF gücü, zamanlama ve son nokta mantığına sahiptir. Ayrıca “sessiz” detayları da içerir: purge süreleri, wafer taşıma davranışı ve odanın ilk waferdan önce nasıl hazırlandığı.

Reçeteler neden değişmeye devam eder

Çipler yeni düğümlere geçtiğinde, fablar genellikle yeni malzemeler ve yeni 3B şekiller tanıtır—çoğu zaman aynı anda. Düz bir yüzeyde işe yarayan bir film derin, dar özelliklerde farklı davranabilir. Önceden yeterli olan bir aşındırma adımı yeni tanıtılan bir liner veya bariyere zarar vermeye başlayabilir.

İşte reçetelerin evrilme nedeni: cihaz hedefleri değişir (hız, güç, güvenilirlik), geometri sıkılaşır ve entegrasyon kısıtlamaları artar. Süreç geliştirme, ölçüm yapma ve yeniden ayarlamanın uzun soluklu bir döngüsü haline gelir—bazen ancak binlerce wafer sonra ortaya çıkan sorunları çözmek için.

Tekrarlanabilirlik, eşleşme ve temiz kalma

Yüksek hacimli üretimde tek bir odanın bir kez iyi sonuç üretmesi yetmez. Tekrarlanabilirlik, aynı reçetenin diskten diske aynı sonucu vermesi demektir. Araçlar arası eşleşme ise bir reçetenin başka bir araca veya başka bir fabe taşındığında yine aynı kalınlık, profil ve uniformite sınırları içinde sonuç vermesini gerektirir—aksi halde üretim planlaması ve verim zarar görür.

Kontaminasyon kontrolü bu gerçeğin parçasıdır. Odalar zamanla iç yüzeylerde film biriktikçe “yaşlanır”, bu da plazma koşullarını ve partikül riskini etkiler. Fablarda süreç stabilitesini korumak için oda koşullandırma, sezonlama çalışmaları, temizleme ve önleyici bakım programlarına dayanılır. Bu operasyonel bilgi—reçetelerin dakikalar değil aylar boyunca performans göstermesini sağlama—deneyimin biriktiği yerdir.

Neden Araç Üreticileri ve Fablar Birlikte Optimizasyon Yapar

İleri düzey çipler, sadece bir araç alıp kurup “çalıştır” diyerek üretilmez. Kaplama ve aşındırma adımları çipin düzenine, malzeme yığınına ve güvenilirlik hedeflerine sıkı sıkıya bağlıdır; bu yüzden ekipman üretenlerle fabı işletenler birlikte iteratif çalışır.

Teslimat bir çizgi değil, bir döngüdür

Çip tasarımcıları ihtiyaç duydukları yapıları tanımlar (örneğin daha küçük kontaklar, daha uzun via’lar, yeni metal yığınları). Fab içindeki süreç entegrasyon ekipleri bu tasarımı adım adım akışa çevirir: bu katmanı kapla, desenle, aşındır, temizle, tekrarla. Lam Research gibi araç üreticileri sonra bu gereksinimleri gerçek donanım üzerinde üretilebilir reçetelere dönüştürmeye yardımcı olur.

Bu teslimat hızla bir döngüye dönüşür: erken üretimler sorunları (profil sürüklenmesi, kalıntı, kenar pürüzlülüğü, beklenmeyen hasar) ortaya çıkarır ve geri bildirim hem süreç akışına hem de araç ayarlarına gider—bazen oda malzemeleri, plazma kaynakları veya gaz dağıtımı gibi donanım değişikliklerine kadar uzanır.

Malzeme, donanım ve akış üzerinde birlikte optimizasyon

İleri düğümde kaplama veya aşındırmayı izole şekilde optimize edemezsiniz çünkü her adım bir sonraki için başlangıç koşulunu değiştirir. Küçük bir film yoğunluğu kayması aşındırma hızını etkileyebilir; daha agresif bir aşındırma sonraki kaplamanın konformaliteğini bozabilir. Birlikte optimizasyon şu alanları hizalar:

- Malzeme seçimleri (yeni dielektrikler, hardmasklar, bariyer katmanlar)

- Araç kabiliyeti (plazma kimyası, sıcaklık kontrolü, wafer taşıma)

- Süreç sıralaması (çok adımlı aşındırma/kaplama döngüleri, temizlemeler, metroloji noktaları)

Ödünler gerçektir—ve kasıtlı yönetilir

Fablarda sürekli olarak verim vs. hız dengesi yapılır: daha hızlı işlem varyabiliteyi artırabilir, oysa ultra sıkı kontrol saatlik wafer sayısını azaltabilir. Benzer şekilde, selektivite vs. hasar sürekli bir gerilimdir: bir malzemeyi güçlü şekilde tercih eden bir aşındırma daha sert koşullar gerektirebilir ve bu da pürüzlülük veya kusur riskini yükseltebilir.

Entegrasyon desteği ürünün bir parçasıdır

Sağlanan değerin önemli bir kısmı devam eden entegrasyon desteğidir—saha sorun giderme, odalar arası performans eşleştirme, sapmaları azaltma ve verim düştüğünde hızlı toparlanmaya yardım etme. Yüksek hacimli üretimde bu ortaklık bir aracın teknik özellik tablosu kadar önemli olabilir.

Araç Kabiliyetinden Fab Çıktısına: Güvenilirlik ve Çalışır Kalma Süresi Önemlidir

Ship changes with rollback

Gereksinimler ramp sırasında değiştiğinde değişiklikleri güvenle test etmek için snapshot ve geri alma kullanın.

Bir kaplama veya aşındırma aracı özellik sayfasında etkileyici görünebilir—ta ki 7/24, binlerce wafer ile aynı sonucu vermesi gerekene kadar. Yüksek hacimli üretimde güvenilirlik ve çalışma süresi "iyi olur" değil, doğrudan fabın kaç tane iyi wafer gönderebileceğini belirleyen unsurlardır.

Sıkı kontrol tüm noktadadır

Kaplama ve aşındırma süreç kararlılığıyla yaşar veya ölür. Gaz akışlarında, oda basıncında, plazma gücünde veya sıcaklıkta küçük sürüklenmeler film kalınlığını, yan duvar açılarını veya hasar seviyelerini değiştirebilir—bir çalışan reçeteyi verim kaybına dönüştürebilir.

İşte bu yüzden gelişmiş araçlar (Lam Research sistemleri dahil) tekrarlanabilir donanıma yoğun yatırım yapar: stabil RF beslemesi, hassas kütle akış kontrolü, termal yönetim ve sapmaları erken yakalayabilecek sensörler.

Çıktı fizikten çok bakımdır

Süreç mükemmel olsa bile, araçlar sık sık kapalıysa üretim zarar görür. Gerçek fab çıktısını şekillendiren unsurlar:

- Planlı bakım aralıkları (temizlik, oda sezonlaması, kit değişimleri)

- Plansız duruşlar (partikül olayları, plazma kararsızlığı, pompa sorunları)

- Parça lojistiği (doğru sarf malzemelerin sahada olması)

Servisi kolay bir araç ve sağlam yedek parça planlaması daha fazla odayı çalışır tutar ve daha fazla lotu hareket ettirir.

Güvenilirlik maliyet ve takvim demektir

Daha yüksek çalışma süresi genellikle bir wafer maliyetini düşürür: daha az işçi başı boşta kalma, pahalı temizoda alanının daha iyi kullanımı ve yeniden işleme harcanan zamanın azalması. Ayrıca, sürekli kullanılabilirlik teslimat takvimlerini öngörülebilir kılar; bu, ardışık adımların sık kuyruklandığı durumlarda önemlidir.

Bir gerçek daha: laboratuvar demonstrasyonlarından kütle üretimine geçiş araçları farklı zorlar. Uzun üretimler, daha yüksek wafer başlatma oranları ve daha katı kusur bütçeleri zayıf noktaları çabucak açığa çıkar—bu nedenle güvenilirlik mühendisliği “süreç kabiliyeti”nin çekirdeği olur.

Sonraki İzlenecekler: Ölçeklendirme Baskısı ve Bir Sonraki Süreç Darboğazı

Çipler daha küçük düğümlere ve daha fazla 3B yapıya itildikçe, ilerleme giderek daha çok yüzlerce kez tekrarlanan kaplama ve aşındırma adımlarını son derece hassas şekilde tekrarlamaya bağlı hale geliyor. “Bir sonraki darboğaz” genellikle tek bir atılım değil; her döngüyü tutarlı tutmanın kümülatif zorluğu, verimi koruma, değişkenliği kontrol etme ve yeni süreçleri talebi karşılayacak hızda rampa etme zorluğudur.

Baskının yoğunlaştığı yerler

Aşağıdaki trendler kaplama/aşındırmayı en çok zorlayacak gibi görünüyor:

- Yeni cihaz mimarileri (GAA/nanosheet, CFET): daha sıkı boşluklar ve daha ince katmanlar küçük kalınlık veya derinlik hatalarına karşı daha hassastır.

- Arka yüz güç iletimi: yeni yüzeyler, yeni entegrasyon adımları ve ön yüz cihazlarını etkilemeden yönetilmesi gereken yeni hata modları ekler.

- Seçici işlemler: “buraya depozite et, oraya etme” ve “bunu aşındır, şunu etme” gibi işlemlere daha fazla güven, selektivite ve kusur kontrolü çıtasını yükseltir.

- Malzeme karmaşıklığı: daha egzotik filmler, linerlar ve bariyerler, uniform, düşük kusurlu ve aşağı akışla uyumlu olmalıdır.

- Rampa hızı beklentileri: düğüm geçişleri sadece kabiliyetle değil, yüksek hacimde verimin ne kadar çabuk stabil hale geldiğiyle değerlendirilir.

Teknik olmayan okuyucular için kısa kontrol listesi

Araç tedarikçilerini veya fab yaklaşımlarını (Lam Research ve rakipleri dahil) karşılaştırırken sonuçlara odaklanın:

- Verim iyileştirmesi: Süreç büyük kusurları ölçekle azaltıyor mu?

- Değişkenlik kontrolü: Wafer içi ve waferlar arası sonuçlar ne kadar sıkı?

- Rampa hızı: Yeni bir düğüm ne kadar çabuk kararlı, yüksek hacimli üretime ulaşabiliyor?

- Tekrarlanabilirlik ve çalışma süresi: Araçlar uzun süre aynı kalitede mi çalışıyor, minimum duruşla?

Daha derine inmek isterseniz, ilgili açıklayıcı yazılara /blog üzerinden bakabilirsiniz. Eğer seçenekleri değerlendiriyorsanız—veya verim, sapmalar ve rampa metriklerini analiz etmek için dahili araçlar inşa ediyorsanız—maliyet, hız ve kabiliyet hakkında nasıl düşündüğümüzü görmek için /pricing bölümüne bakabilirsiniz (örneğin Koder.ai gibi sohbet tabanlı bir platformun eski, hantal yazılım süreçlerini ne zaman değiştirebileceğini değerlendirmek için faydalı olabilir).

SSS

What are deposition and etch in chip manufacturing, in plain terms?

Deposition, "ekleme" adımıdır: araçlar ultra-ince filmler (metaller, dielektrikler, bariyerler, astarlar, hardmasklar) bırakır. Etch ise "çıkarma" adımıdır: desenleri aktarmak ve yapı oluşturmak için belirli malzemeleri seçici şekilde aşındırır.

İlerleme, nanometre ölçeğinde kalınlık, şekil ve ara yüzler üzerinde kontrol sağlamaya bağlı olduğundan, kaplama/aşındırma kalitesi doğrudan performans ve verimi etkiler.

What does “leading-edge” mean in semiconductor manufacturing?

“Leading-edge” genellikle en gelişmiş düğümleri, yani yüksek hacimli üretimde en yeni cihaz yapılarına ve malzemelere rastlanan aşamaları ifade eder.

Bu, pazarlama etiketinden ziyade daralan süreç pencereleri ve küçük değişimlere karşı yüksek hassasiyetle çalışmayı ifade eder.

Why do deposition and etch steps keep multiplying as nodes shrink?

Modern çipler şu döngülerle inşa edildiği için kaplama ve aşındırma adımları çoğalır:

- Kapla bir film

- Desenle (litografi + maske)

- Aşındır deseni aktar

- Strip/kazı ve tekrar et

Özellikle daha küçük özelliklerde ve karmaşık yığınlarda, tek bir “katman” genellikle hedef boyutları ve profilleri yakalamak için gerektirir.

What is conformality, and why is it so important for 3D structures?

Konformalite, bir filmin 3B yapıların üst yüzey, yan duvar ve dip bölgelerini ne kadar eşit kapladığını anlatır.

Önemi şundan gelir: düzensiz kaplama

- dar açıklıkları tıkayabilir

- zayıf bariyerler oluşturarak sızıntıya veya difüzyona yol açabilir

- sonraki aşındırma adımlarında eksik doluma veya hatalara neden olabilir

Konformalite kritik olduğunda genellikle gibi teknikler kullanılır.

What is etch selectivity, and what goes wrong when it’s poor?

Selektivite, bir aşındırmanın bir malzemeyi diğerine göre ne kadar hızlı kaldırdığını (genellikle bir “etch stop” katmanı ile karşılaştırma) ifade eder.

Yüksek selektivite sayesinde:

- hedef katman temizlenir, altındaki katman inceltilmez

- kritik boyutlar korunur

- aşındırma hasarından kaynaklanan sızıntı ve güvenilirlik riskleri azalır

Why do fabs use hardmask stacks instead of etching directly through photoresist?

Fotoresist genellikle modern derin ve hassas aşındırmaları sürdürecek kadar kalın veya dayanıklı değildir. Bir hardmask yığını, resist desenini hedef filmin üzerine aktarmada daha dayanıklı bir “çevirmen” görevi görür.

Basitleştirilmiş akış şu şekildedir:

- hardmask katmanları depozite edilir

- resist deseni hardmask'e aktarılır

- hardmask deseni hedef filme aktarılır

- strip/temizleme yapılır

Hardmask seçimi ile yönlendirilir.

How does multi-patterning increase deposition and etch demand?

Multi-patterning, tek bir litografi geçişinin nihai aralığı güvenilir şekilde tanımlayamadığı durumlarda yoğun desenleri birden fazla maruz bırakma ve aktarım adımına bölmektir.

Bu, spacer veya mandrel oluşturma gibi destekleyici adımları ekler; böylece tek bir nihai özelliği oluşturmak için gereken kaplama + aşındırma sayısını (ve temizlikleri ile metrolojiyi) artırır.

Why are high aspect ratio features so challenging for etch and deposition?

Yüksek en-boy oranlı yapılar (derinlik genişliğe göre çok büyük) şu sorunları zorlaştırır:

- reaktiflerin ve iyonların dibe eşit ulaşamaması

- artık ürünlerin uzaklaştırılmasının zorlaşması

- yoğun ve seyrek bölgelerde farklı aşındırma hızları (microloading)

Bunlar profil sorunları (notching/footing), kalıntı, pürüzlülük ve değişkenlik riskini artırır; dolayısıyla süreç ayarı daha sıkı olur.

How do deposition and etch affect yield and defects?

Verim, wafer üzerindeki işe yarar die oranıdır. Kaplama ve aşındırma şu şekillerde verimi etkiler:

- Açıklar (opens): hattın incelmesi veya kopması sonucu akım akmaz

- Kısa devreler (shorts): ayrılması gereken iki özellik birbirine temas eder

- Sızıntı (leakage): yalıtkan katmanlar fazla ince, gözenekli veya hasarlı olur

Özellikle ileri düğümlerde, kalınlık veya profildeki küçük sapmalar bile cihazları spesifikasyon dışına itebilir.

Why does manufacturing know-how “compound,” and how does that relate to Lam Research?

Bir aracın özellikleri önemli olsa da, üretimde farklılaştıran çoğunlukla süreç bilgisidir: reçeteler, entegrasyon sıralamaları, kusur öğrenimi ve araçlar arası eşleştirme.

Bu bilgi birikimi, her düğümde şu konularda birikerek ilerler:

- karmaşık topografide film büyüme davranışları

- plazmanın profil ve hasar etkileri

- uzun çalışmalarda odaların stabil tutulması

Bu yüzden gibi ekipman tedarikçileri, ileri düzey üretimde stratejik öneme sahip olabilir.