May 04, 2025·8 min

Lam Research and the Compounding Advantage in Chipmaking

How deposition and etch tools shape leading-edge chips, why process know-how builds on itself over time, and what that means for yields, nodes, and scaling.

How deposition and etch tools shape leading-edge chips, why process know-how builds on itself over time, and what that means for yields, nodes, and scaling.

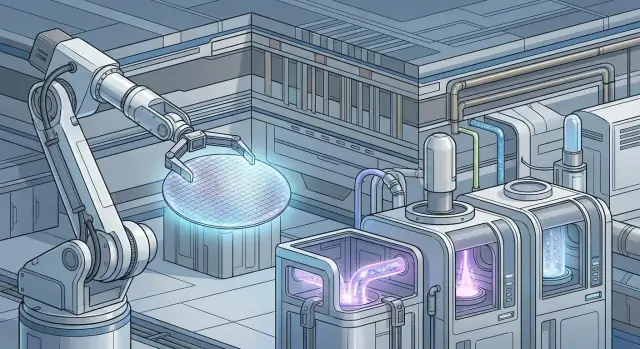

If you strip chipmaking down to its most repeatable moves, two actions show up again and again: deposition and etch.

Deposition is the “add” step. Tools lay down ultra-thin films—conductors, insulators, or special barrier layers—on a wafer, sometimes just a few atoms at a time. Etch is the “remove” step. Tools selectively carve material away to create the tiny features that become transistors and wiring, ideally without harming the layers underneath.

As chips have scaled, these two steps have become the primary knobs engineers use to control what matters most at nanometer dimensions: thickness, shape, and interfaces. That’s why equipment companies such as Lam Research sit close to the heart of leading-edge manufacturing.

“Leading-edge” generally refers to the most advanced, high-volume production nodes—where density, power, and performance targets are most aggressive, and the margin for error is smallest. It’s not just about a marketing number; it’s where new device structures and new materials show up first.

Tool capability matters (uniformity, selectivity, damage control, throughput). But process know-how matters just as much: the recipes, integration tricks, metrology feedback, and defect-learning that turn a great tool into a stable, high-yield factory process.

That advantage compounds over technology generations because each new node doesn’t start from zero—it builds on prior learning about how films grow, how plasmas behave, and how tiny variations create big yield swings.

To see why deposition and etch cycles keep multiplying, we’ll look at:

A modern chip isn’t “machined” from a block of silicon. It’s assembled—more like a microscopic layer cake—by repeatedly adding ultra-thin films, patterning them, and selectively removing what you don’t want. Do that hundreds of times, and you end up with transistors, wiring, and insulating barriers stacked and intertwined in 3D.

At a high level, chipmaking cycles through a familiar rhythm:

Each loop creates one “slice” of the final device—gate structures, contact holes, or interconnect lines—until the chip’s logic and memory emerge from the stack.

When features are measured in single-digit nanometers, thickness and shape control stop being “nice to have.” A film that’s slightly too thick can pinch off a narrow opening; an etch that’s slightly too aggressive can widen a line or nick an underlying layer. Even small profile changes—sidewall angle, corner rounding, surface roughness—can shift how electricity flows.

Manufacturing is organized into process steps (specific deposition/etch operations) that must run inside a process window—the range of settings where results are consistently acceptable. As chips get denser, those windows shrink. And because later layers build on earlier ones, a small deviation can cascade into misalignment, shorts, opens, and ultimately lower yield.

Deposition is the “adding material” half of chipmaking: building ultra-thin films on a wafer so later steps can pattern, protect, or electrically isolate what’s underneath. These films aren’t decorative—each one is chosen for a specific job, and it has to work reliably across billions of tiny features.

Chemical Vapor Deposition (CVD) uses reactive gases that form a solid film on the wafer surface. It’s widely used for many dielectric and some conductive layers because it can cover large areas efficiently and with good uniformity.

Physical Vapor Deposition (PVD) (often “sputtering”) knocks atoms off a target material and deposits them onto the wafer. PVD is common for metals and hardmask materials, especially when you want a dense film—but it can struggle to coat the sidewalls of very deep, narrow structures.

Atomic Layer Deposition (ALD) deposits material one molecular “dose” at a time through self-limiting surface reactions. It’s slower, but it excels when control and coverage matter more than speed—particularly in the tightest 3D features.

As chips moved to fins, trenches, and vertical holes, deposition stopped being a simple “paint the top” problem. Conformality describes how evenly a film coats the top surface, sidewalls, and bottom of a feature.

If a layer is thin on the sidewall or pinches off at the opening, you can get electrical leakage, poor fill, or failures in later etch steps. High conformality is crucial for deep, narrow features where there’s very little margin for error.

Even if the thickness is correct, the film must meet several practical requirements:

At the leading edge, deposition isn’t just “adding a film.” It’s precise materials engineering, tuned so every subsequent etch and pattern step behaves predictably.

Etch is the “subtractive” half of chipmaking: after a film is deposited and patterned with resist, etch removes exposed material to transfer that pattern into the layer below. The trick is that you rarely want to remove everything—you want to remove one specific material quickly while stopping on another. That property is called selectivity, and it’s central to why leading-edge fabs invest so much in etch process know-how (and why tool vendors like Lam Research spend years refining it).

A modern stack might include silicon, silicon oxide, silicon nitride, metals, and hard masks. During etch, you may need to clear one layer cleanly while leaving the “etch stop” layer intact. Poor selectivity can thin critical layers, shift transistor dimensions, or create leakage paths that hurt yield.

Most advanced etching uses a plasma: a low-pressure gas energized into reactive species.

Two things happen at once:

Balancing these is the art: too much chemistry can undercut features; too much ion energy can damage what you’re trying to keep.

Process teams usually chase a few outcomes:

Even when the recipe is “right,” real wafers fight back:

At leading nodes, managing these details is often the difference between a lab demo and high-volume manufacturing.

When people picture chip scaling, they often imagine a single breakthrough machine that “prints” ever-smaller lines. In practice, pattern transfer is constrained by the whole chain—resist, hardmasks, etch selectivity, film stress, and cleaning—not one magic tool.

Photoresist is great for capturing a pattern, but it’s usually too thin and too fragile to survive the deep, precise etches required in modern devices. So fabs build hardmask stacks—carefully chosen films deposited on top of the target layer.

A simplified flow looks like this:

Each deposited film is selected not just for what it is, but for how it behaves during the next etch: how fast it etches compared with neighboring layers, how much roughness it creates, and how well it holds its shape.

As critical dimensions shrink beyond what a single lithography pass can reliably define, fabs use multi-patterning—splitting one dense pattern into multiple exposures and transfers. That doesn’t just add lithography steps; it multiplies the supporting deposition/etch loops for spacers, mandrels, trims, and cut masks.

The punchline: the “pattern” on a leading-edge chip may be the result of several cycles of depositing films and etching them back with tight control.

Because every step changes the starting conditions for the next, the best results come from tuning the full sequence—materials, plasma conditions, chamber cleanliness, and cleans—as a single system. A small improvement in one etch can be erased (or amplified) by the next deposition, which is why process integration know-how becomes a differentiator over time.

Planar transistors were mostly “flat,” which made many steps feel like painting and trimming a surface. Scaling pushed the industry into 3D: first FinFETs (a vertical “fin” wrapped by the gate), and now gate-all-around (GAA) concepts where the gate fully surrounds the channel (often as stacked nanosheets).

Once features have sidewalls, corners, and deep cavities, deposition stops being a simple “coat the top.” Films must be conformal—nearly the same thickness on the bottom of a trench as on the top surface.

That’s why techniques like ALD and carefully tuned CVD steps matter more at the leading edge: a few atoms too thin on a sidewall can become higher resistance, poorer reliability, or a weak barrier that lets materials diffuse where they shouldn’t.

Etch must form the right profile: straight walls, clean bottoms, minimal roughness, and selective removal of one material without chewing up the layer underneath. In dense 3D patterns, even small “over-etch” can nick critical regions, while “under-etch” leaves residue that blocks later deposition.

Many modern structures are high aspect ratio—very deep compared with how narrow they are. Getting uniform results across billions of these features is hard because reactants, ions, and byproducts don’t move evenly in and out of tight spaces. Problems like microloading (different etch rates depending on local pattern density) and sidewall damage become more likely.

GAA and advanced interconnects bring more complex material stacks and ultra-thin interfaces. That raises the bar for surface preparation: pre-cleans, gentle plasma treatments, and interface control before the next deposition step. When the “surface” is only a few atomic layers thick, process know-how becomes the difference between a device that works and one that quietly fails later.

“Yield” is simply the share of chips on a wafer that work as intended. If a wafer holds thousands of chips, a tiny change in defect rate can translate into hundreds more sellable parts. That’s why manufacturers obsess over what sounds like small numbers—because at scale, small improvements become real output.

Many yield losses don’t look dramatic under a microscope; they show up as electrical failures. A few common examples:

Deposition and etch steps can influence all of these. A film that’s slightly off in thickness, composition, or uniformity might still “look fine,” but it can shift transistor behavior enough to miss speed or power targets.

Even when there’s no obvious defect, variation across the wafer (or from wafer to wafer) creates chips that behave inconsistently. One corner runs hotter, another corner is slower, and suddenly the product binning changes—or the part fails. Tight control of deposition rates, plasma conditions, and etch selectivity reduces these swings.

Modern fabs don’t tune processes by intuition. They rely on metrology (measuring thickness, critical dimensions, profile shape, uniformity) and inspection (finding particles, pattern defects, edge issues). The results feed back into process adjustments:

In practice, this also creates a software problem: stitching together data from tools, metrology, and inspection into something engineers can act on quickly. Teams often build internal dashboards, alerting, and “what changed?” tools to shorten the loop from signal to fix. Platforms like Koder.ai can help here by letting process and data teams spin up lightweight web apps from chat—useful for integrating yield KPIs, excursion notes, and run history without waiting on a long traditional development cycle.

The most valuable know-how is incremental: every node teaches what causes certain defects, which settings drift with time, and which combinations are stable. Those lessons carry forward—so the next node starts with a better playbook, not a blank sheet.

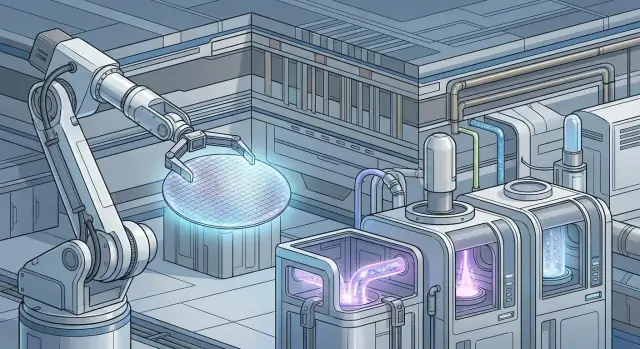

A deposition or etch tool doesn’t run on a single “setting.” It runs on a recipe—a structured sequence of steps that defines how the process happens over time. A recipe can include multiple phases (stabilize, pre-clean, main step, post-treatment), each with its own gas flows, pressure, temperature, RF power, timing, and endpoint logic. It also includes the “quiet” details: purge times, wafer handling behavior, and how the chamber is prepared before the first wafer.

As chips move to new nodes, fabs introduce new materials and new 3D shapes—often at the same time. A film that worked on a flat surface may behave differently on deep, narrow features. An etch step that was selective enough last generation may start damaging a newly introduced liner or barrier.

That’s why recipes evolve: device targets shift (speed, power, reliability), geometry gets tighter, and integration constraints multiply. Process development becomes a long-running cycle of tuning, measuring, and re-tuning—sometimes to solve problems that only appear after thousands of wafers.

In high-volume manufacturing, it’s not enough for one chamber to produce great results once. Repeatability means the same recipe yields the same outcome wafer after wafer. Tool-to-tool matching means that a recipe transferred to another tool (or another fab) still hits the same thickness, profile, and uniformity within tight limits—otherwise production planning and yield suffer.

Contamination control is part of this reality. Chambers “age” as films build up on internal surfaces, affecting plasma conditions and particle risk. Fabs rely on chamber conditioning, seasoning runs, cleans, and preventative maintenance schedules so the process stays stable over time. That operational know-how—how to keep recipes performing for months, not minutes—is where experience compounds.

Leading-edge chips aren’t manufactured by simply buying a tool, installing it, and pressing “run.” Deposition and etch steps are tightly coupled to the chip’s layout, materials stack, and reliability targets, so the people building the equipment and the people running the fab end up iterating together.

Chip designers define the structures they need (for example, smaller contacts, taller vias, new metal stacks). Process integration teams inside the fab translate that design into a step-by-step flow: deposit this layer, pattern it, etch it, clean it, repeat. Tool makers like Lam Research then help turn those requirements into manufacturable recipes on real hardware.

That handoff quickly becomes a loop: early runs reveal issues (profile drift, residue, line-edge roughness, unexpected damage), and feedback goes back to both the process flow and the tool settings—sometimes even to hardware options such as chamber materials, plasma sources, or gas delivery.

At the leading edge, you can’t optimize deposition or etch in isolation because each step changes the starting condition for the next one. A small shift in film density can alter etch rate; a more aggressive etch can make downstream deposition less conformal. Co-optimization aligns:

Fabs constantly balance throughput vs. precision: faster processing can increase variability, while ultra-tight control may reduce wafers per hour. Similarly, selectivity vs. damage is a recurring tension: an etch that strongly prefers one material may require harsher conditions that risk roughness or defectivity.

A key part of the value delivered is ongoing integration support—on-site troubleshooting, matching performance across chambers, reducing excursions, and helping recover quickly when yields move. For high-volume manufacturing, that partnership can matter as much as the tool’s spec sheet.

“Compounding” in chip manufacturing isn’t just about buying better tools. It’s the way small, practical advantages accumulate when teams repeatedly run the same classes of processes—deposition and etch—across multiple technology generations.

In this context, compounding is the flywheel of:

None of this guarantees success, but it typically shortens the time from “works in a demo” to “works every day in production.”

When a fab ramps a new node, it hits predictable challenges: variability, defects, edge cases, and tool-to-tool matching. Each issue solved creates reusable knowledge—how to tune plasma conditions without damaging sensitive layers, which chamber cleans prevent particle spikes, or how to detect drift before it shows up as yield loss.

Over time, those learning loops can make later ramps smoother. Teams start closer to the destination because they’ve already mapped many of the dead ends.

Even if another approach looks similar on paper, switching can be expensive and risky:

That’s why manufacturing know-how tends to persist and build: once a process flow is stable, the incentive is to refine it—not restart it—unless the benefits are clearly worth the re-learning.

A deposition or etch tool can look amazing on a spec sheet—until it has to run 24/7, on thousands of wafers, with the same results every time. In high-volume manufacturing, reliability and uptime are not “nice to have.” They directly determine how many good wafers a fab can ship.

Deposition and etch live and die by process stability. Small drift in gas flows, chamber pressure, plasma power, or temperature can shift film thickness, sidewall angles, or damage levels—turning a working recipe into yield loss.

That’s why leading tools (including Lam Research systems) invest heavily in repeatable hardware: stable RF delivery, precise mass flow control, thermal management, and sensors that can catch excursions early.

Even if the process is perfect, production suffers when tools are frequently down. Real fab output is shaped by:

A tool that’s easier to service—and supported by strong spares forecasting—keeps more chambers running and more lots moving.

Higher uptime typically lowers cost per wafer: fewer idle operators, better utilization of expensive cleanroom space, and less time lost to rework. Just as important, consistent availability makes delivery schedules predictable, which matters when downstream steps are tightly queued.

One more reality: scaling from lab demos to mass production stresses tools differently. Extended runs, higher wafer starts, and stricter defect budgets expose weak points quickly—so reliability engineering becomes a core part of “process capability.”

As chips push into smaller nodes and more 3D structures, progress increasingly hinges on repeating deposition and etch steps with extreme precision—often hundreds of times in one device stack. The “next bottleneck” usually isn’t a single breakthrough, but the cumulative difficulty of keeping every cycle consistent while maintaining yield, controlling variability, and ramping new processes fast enough to meet demand.

Several trends are likely to stress deposition/etch the most:

When comparing tool vendors or fab approaches (including Lam Research and peers), focus on outcomes:

To go deeper, browse related explainers on /blog. If you’re evaluating options—or building internal tooling to analyze yield, excursions, and ramp metrics—see /pricing for how we think about cost, speed, and capability (including when a build-with-chat platform like Koder.ai can replace a slower, legacy software pipeline).

Deposition is the “add” step: tools lay down ultra-thin films (metals, dielectrics, barriers, liners, hardmasks). Etch is the “remove” step: tools selectively carve specific materials to transfer patterns and form features.

Scaling depends on controlling thickness, shape, and interfaces at nanometer dimensions, so deposition/etch quality directly impacts performance and yield.

“Leading-edge” usually means the most advanced nodes in high-volume production, where device structures and materials are newest and tolerances are tight.

It’s less about a marketing label and more about operating with shrinking process windows and higher sensitivity to tiny variations.

Because modern chips are built through repeating loops:

As features get smaller and stacks get more complex, one “layer” often requires to hit the intended dimensions and profiles.

Conformality is how evenly a film coats the top, sidewalls, and bottom of 3D features.

It matters because non-uniform coverage can:

Techniques like ALD are often used when conformality is critical.

Selectivity is how much faster an etch removes one material than another (often an “etch stop” layer).

High selectivity helps you:

Photoresist often can’t survive the depth/precision of modern etches. A hardmask stack acts as a tougher “translator” between the resist pattern and the underlying film.

A typical flow is:

Hardmask choices are driven by .

Multi-patterning splits one dense pattern into multiple pattern-transfer steps when a single lithography pass can’t reliably define the final pitch.

That adds supporting steps such as spacer or mandrel formation, which increases the number of deposition + etch operations (plus cleans and metrology) needed to build one final feature set.

High aspect ratio features (very deep relative to width) make transport harder:

The result is more risk of profile issues (notching/footing), residue, roughness, and variability—so process tuning becomes more stringent.

Yield is the fraction of dies on a wafer that work. Deposition and etch influence yield by driving defects and variability that become electrical failures, such as:

Even “small” drifts in thickness or profile can push devices out of spec at leading-edge dimensions.

A tool’s specs matter, but in production the differentiator is often process know-how: recipes, integration sequencing, defect learning, and tool-to-tool matching.

That know-how compounds because each node builds on prior learning about:

This is why equipment companies like can be strategically important in leading-edge manufacturing.